The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

# SH7764 Group

User's Manual: Hardware

Renesas 32-Bit RISC Microcomputer SuperH<sup>TM</sup> RISC engine Family / SH-4A Series

SH77641 R5S77641

SH77640 R5S77640

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Reneasa Electronics products listed herein, please confirm the latest product information with a Reneasa Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- 2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# **General Precautions on Handling of Product**

#### 1. Treatment of NC Pins

Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are they are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

## 2. Treatment of Unused Input Pins

Note: Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a pass-through current flows internally, and a malfunction may occur.

## 3. Processing before Initialization

Note: When power is first supplied, the product's state is undefined.

The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

## 4. Prohibition of Access to Undefined or Reserved Addresses

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

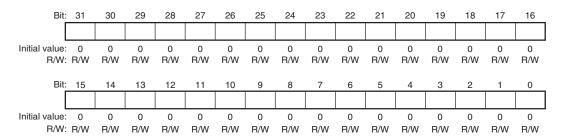

# 5. Reading from/Writing to Reserved Bit of Each Register

Note: Treat the reserved bit of register used in each module as follows except in cases where the specifications for values which are read from or written to the bit are provided in the description.

The bit is always read as 0. The write value should be 0 or one, which has been read immediately before writing.

Writing the value, which has been read immediately before writing has the advantage of preventing the bit from being affected on its extended function when the function is assigned.

# Configuration of This Manual

This manual comprises the following items:

- 1. General Precautions on Handling of Product

- 2. Configuration of This Manual

- 3. Preface

- 4. Contents

- 5. Overview

- 6. Description of Functional Modules

- CPU and System-Control Modules

- On-Chip Peripheral Modules

The configuration of the functional description of each module differs according to the module. However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. Each section includes notes in relation to the descriptions given, and usage notes are given, as required, as the final part of each section.

- 7. Electrical Characteristics

- 8. Appendix

- 9. Main Revisions and Additions in this Edition

- 10. Index

# **Preface**

This LSI is a RISC (Reduced Instruction Set Computer) microcomputer which includes a Renesas original RISC CPU as its core, and the peripheral functions required to configure a system.

Target Users: This manual was written for users who will be using this LSI in the design of

application systems. Users of this manual are expected to understand the fundamentals of electrical circuits, logical circuits, and microcomputers.

Objective: This manual was written to explain the hardware functions and electrical

characteristics of this LSI to the above users.

Notes on reading this manual:

• In order to understand the overall functions of the chip

Read the manual according to the contents. This manual can be roughly categorized into parts

on the CPU, system control functions, peripheral functions and electrical characteristics.

In order to understand the details on FPU functions and each instructions

Read the additional volume, SH-4A Extended Functions Software Manual.

Rules: Bit order: The MSB is on the left and the LSB is on the right.

Number notation: Binary is B'xxxx, hexadecimal is H'xxxx, decimal is xxxx.

Signal notation: An overbar is added to a low-active signal:  $\overline{xxxx}$

## **Abbreviations**

ATAPI ATAPI Controller

CPG Clock Pulse Generator

DMAC Direct Memory Access Controller

E-DMAC Ethernet Controller Direct Memory Access Controller

EtherC Ethernet Controller

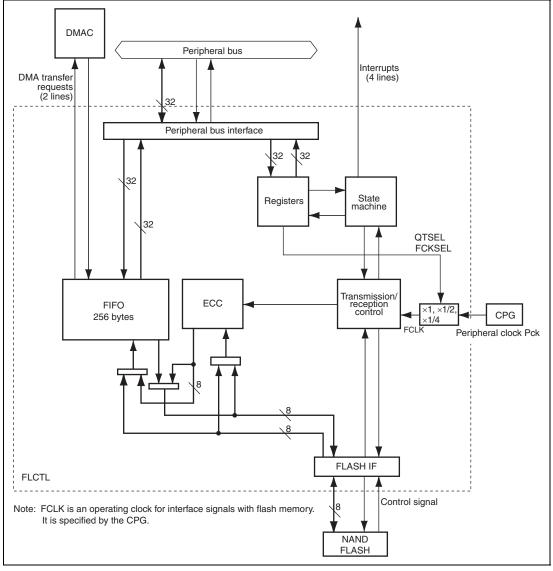

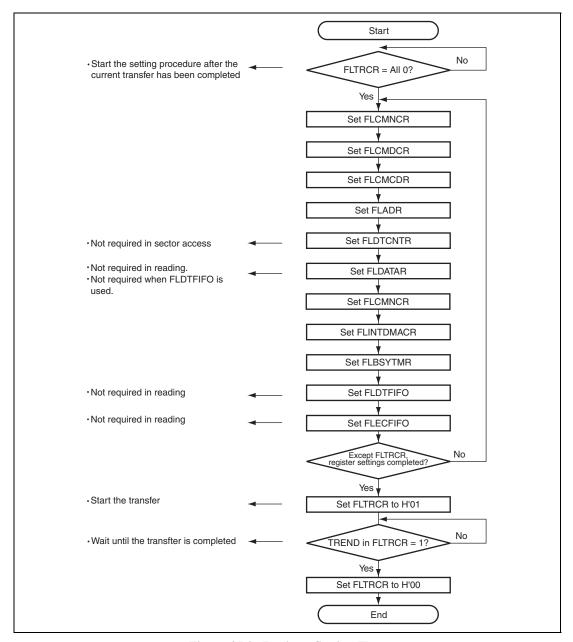

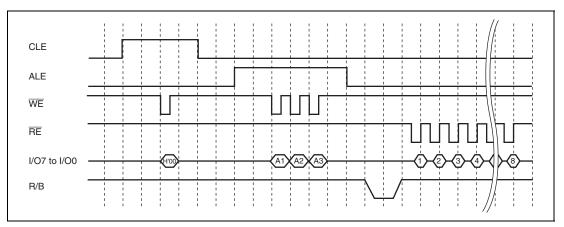

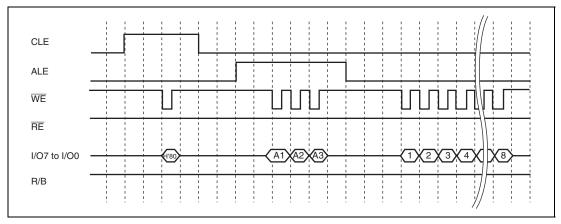

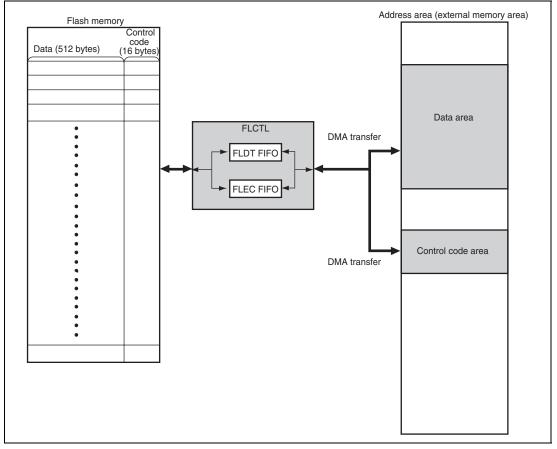

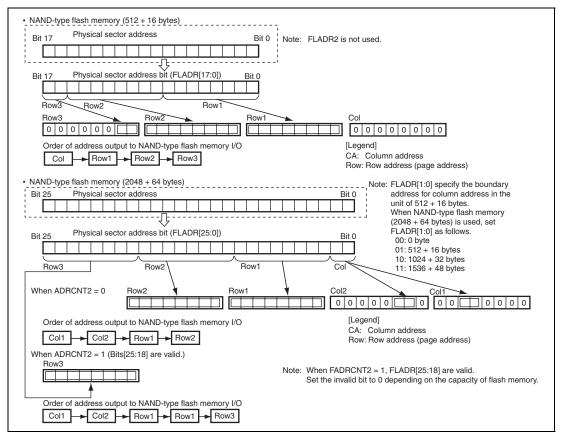

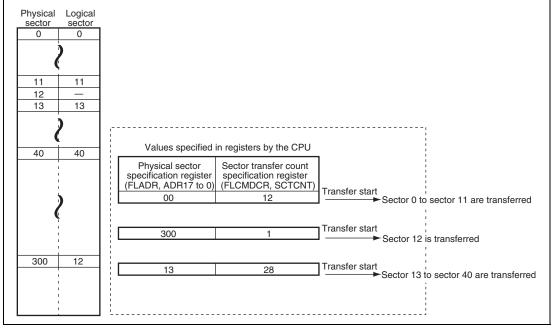

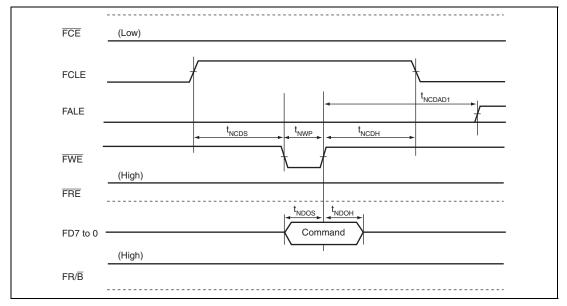

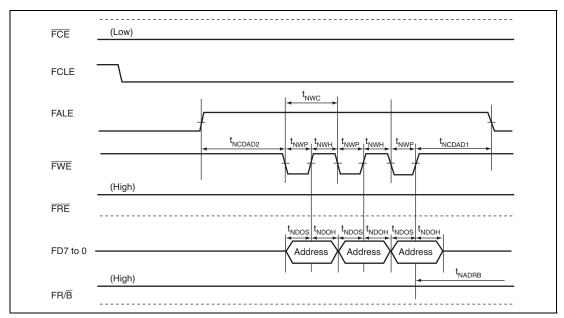

FLCTL NAND Flash Memory Controller

G2D 2D Graphics Engine

GPIO General Purpose I/O

H-UDI User Debugging Interface

IIC I<sup>2</sup>C Bus Interface

INTC Interrupt Controller

MCU Memory Controller Unit

MMU Memory Management Unit

SCIF Serial Communication Interface with FIFO

TMU Timer Unit

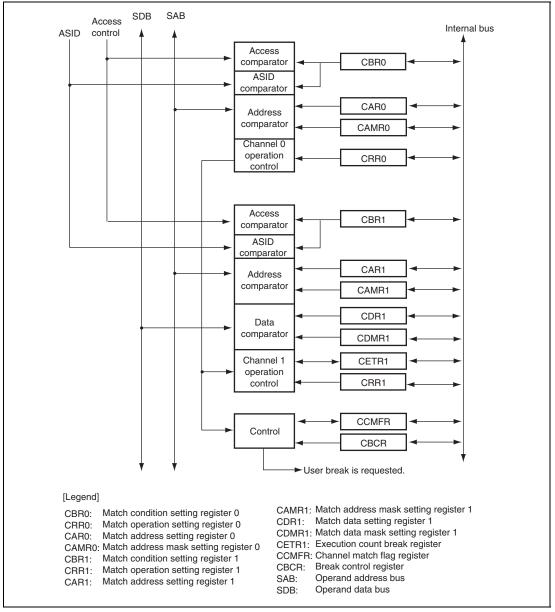

UBC User Break Controller

USB Host/Function Interface

VDC2 Video Display Controller 2

WDT Watchdog Timer and Reset

SSI Serial Sound Interface

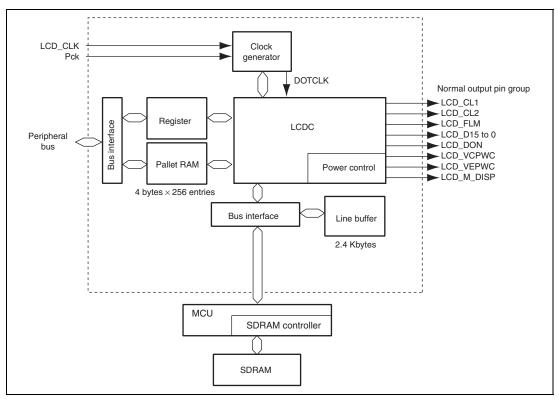

LCDC LCD Controller

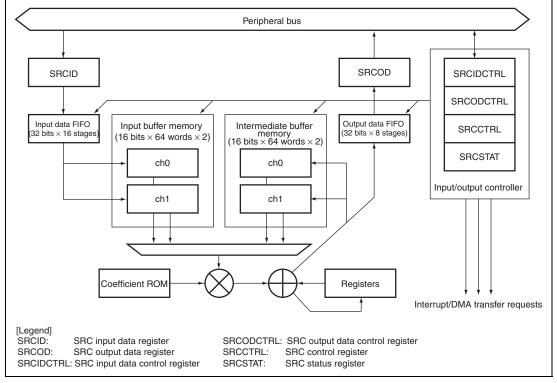

SRC Sampling Rate Converter

bps bits per second

CRC Cyclic Redundancy Check

DMA Direct Memory Access

DMAC Direct Memory Access Controller

Hi-Z High Impedance

I/O Input/Output

LSB Least Significant Bit

MSB Most Significant Bit

NC Non-Connection

PLL Phase Locked Loop

All trademarks and registered trademarks are the property of their respective owners.

# Contents

| Sect | tion 1 Overview                      | 1  |

|------|--------------------------------------|----|

| 1.1  | SH7764 Features                      | 1  |

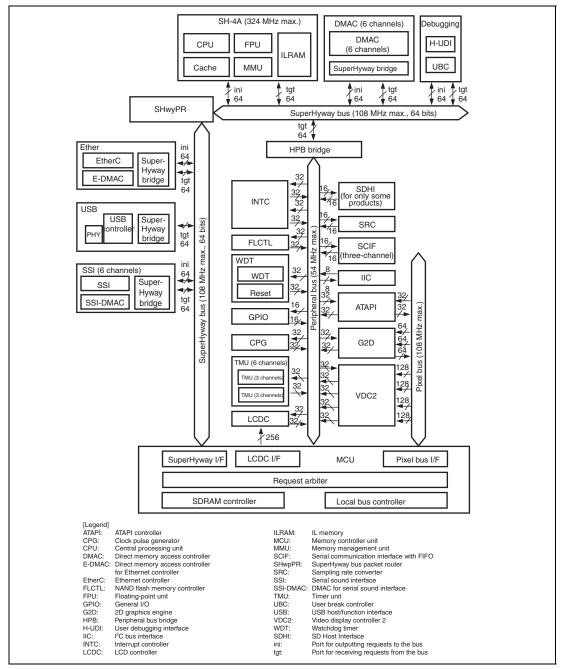

| 1.2  | Block Diagram                        | 12 |

| 1.3  | Pin Arrangement                      | 14 |

| 1.4  | Pin Functions                        | 15 |

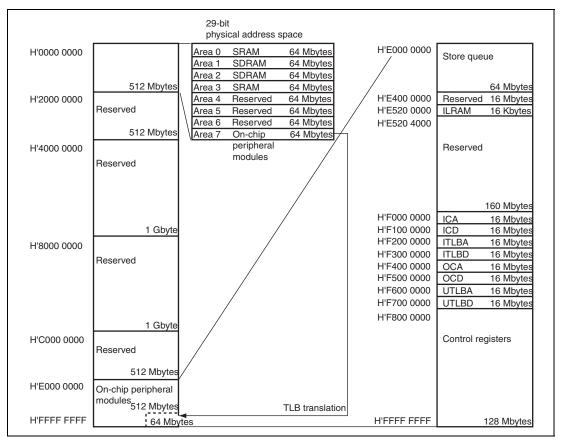

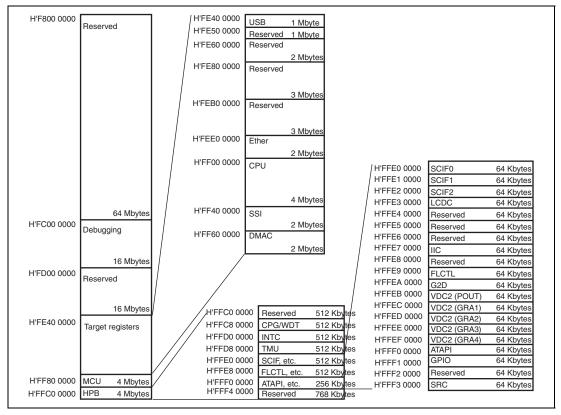

| 1.5  | Address Map                          | 28 |

| Sect | tion 2 Programming Model             | 31 |

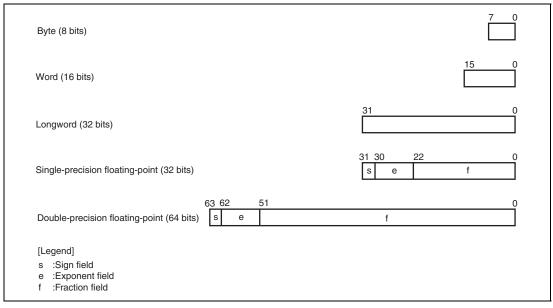

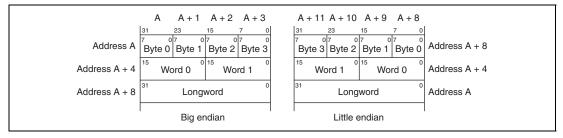

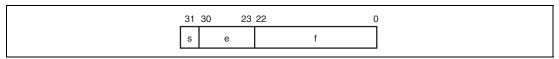

| 2.1  | Data Formats                         | 31 |

| 2.2  | Register Descriptions                | 32 |

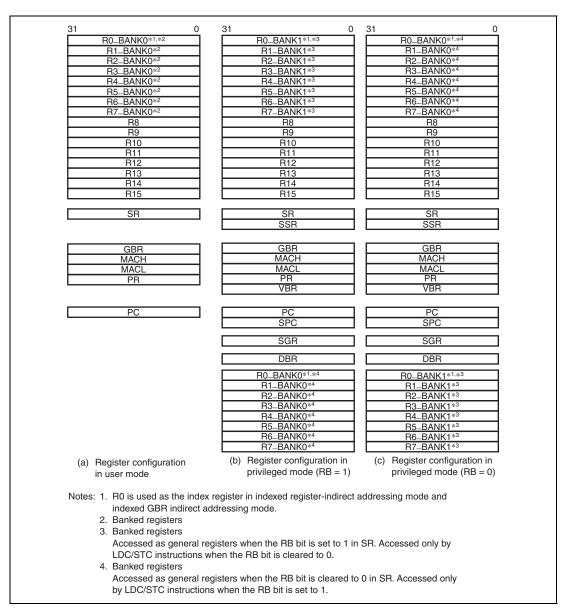

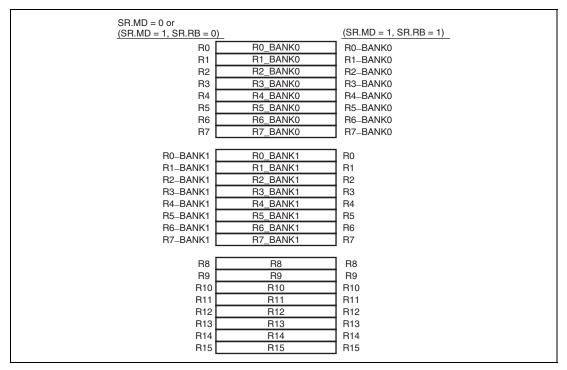

|      | 2.2.1 Privileged Mode and Banks      | 32 |

|      | 2.2.2 General Registers              | 36 |

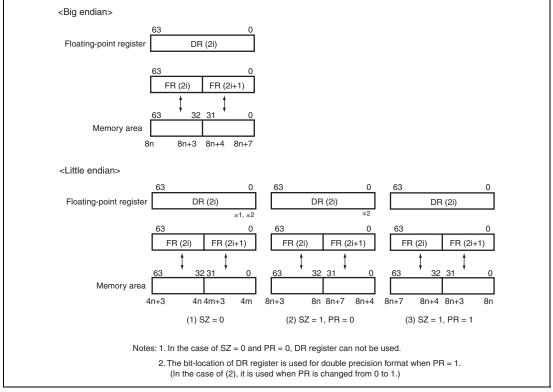

|      | 2.2.3 Floating-Point Registers       | 37 |

|      | 2.2.4 Control Registers              | 39 |

|      | 2.2.5 System Registers               | 41 |

| 2.3  | Memory-Mapped Registers              | 45 |

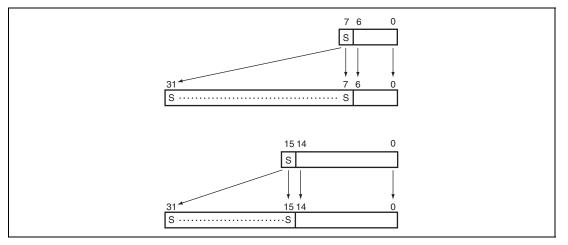

| 2.4  | Data Formats in Registers            | 46 |

| 2.5  | Data Formats in Memory               | 46 |

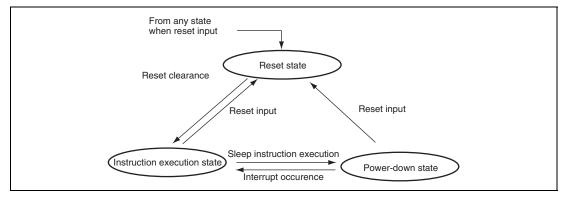

| 2.6  | Processing States                    | 47 |

| 2.7  | Usage Notes                          | 49 |

|      | 2.7.1 Notes on Self-Modifying Code   | 49 |

| Sect | tion 3 Instruction Set               | 51 |

| 3.1  | Execution Environment                | 51 |

| 3.2  | Addressing Modes                     | 53 |

| 3.3  | Instruction Set                      | 58 |

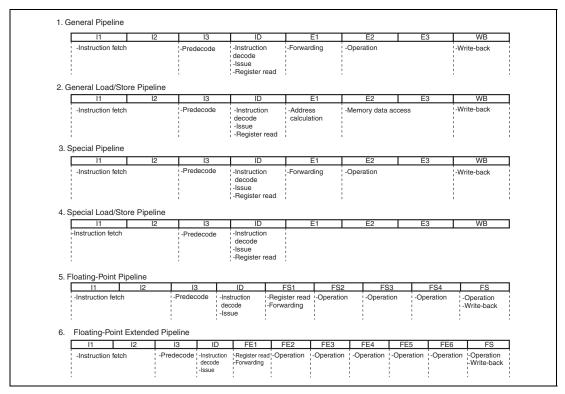

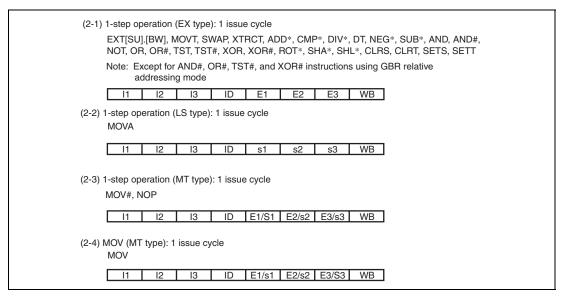

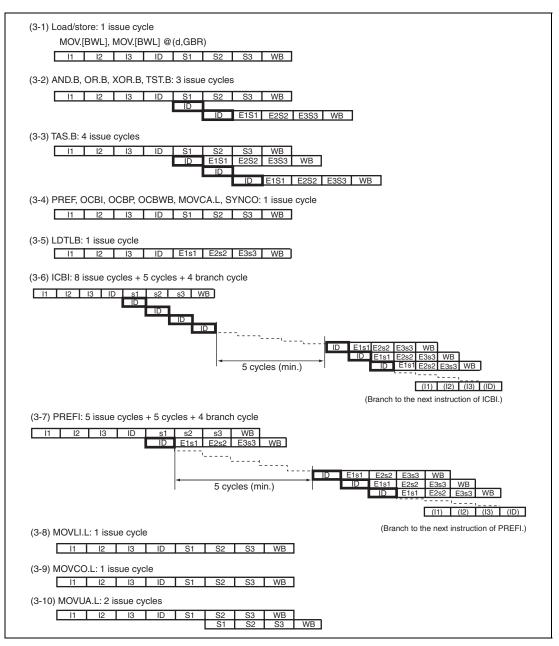

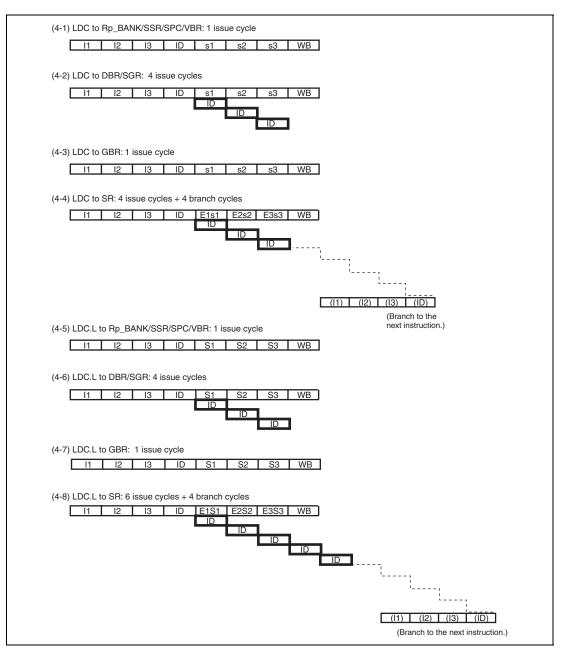

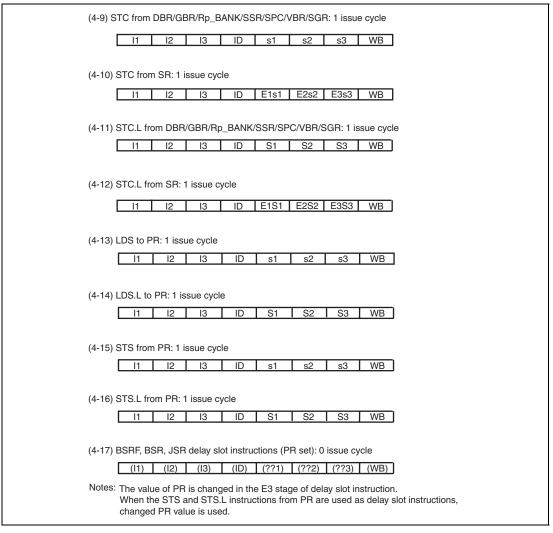

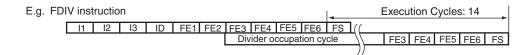

| Sect | tion 4 Pipelining                    | 71 |

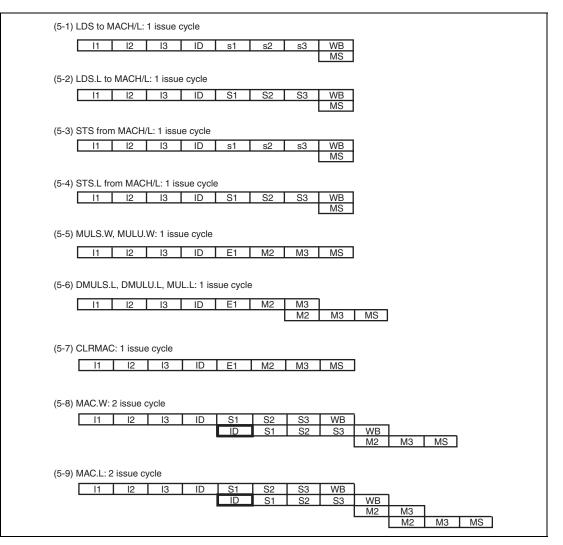

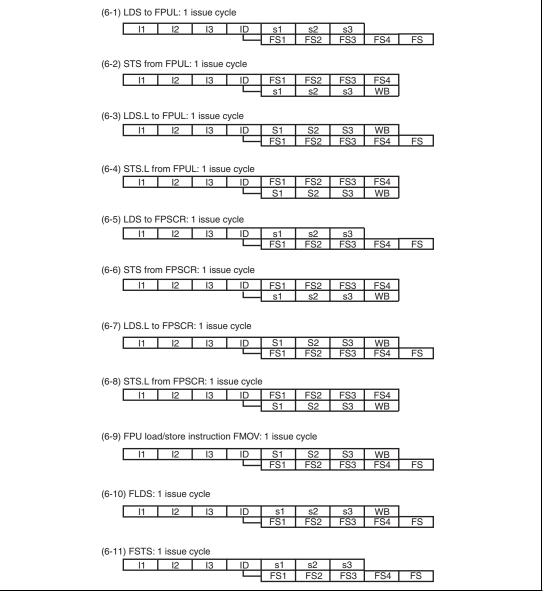

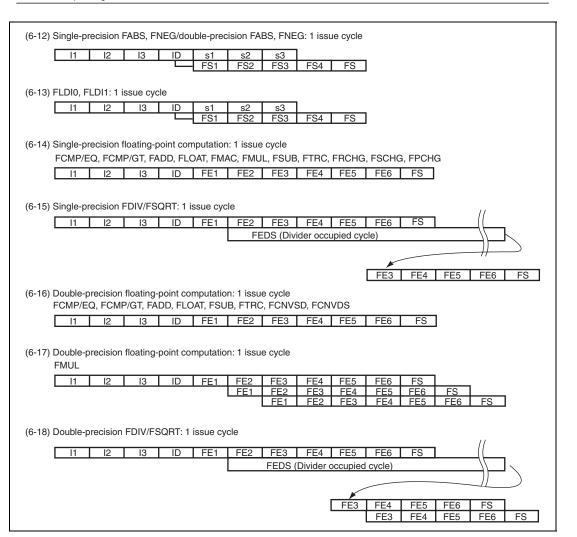

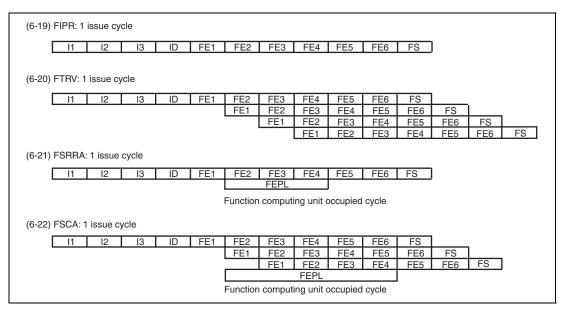

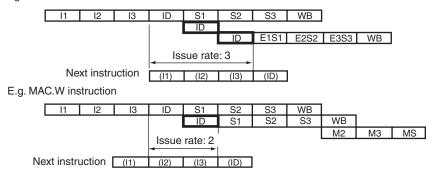

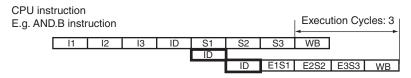

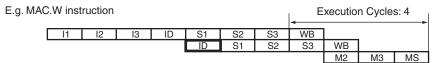

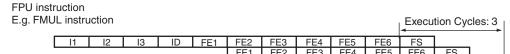

| 4.1  | Pipelines                            | 71 |

| 4.2  | Parallel-Executability               | 82 |

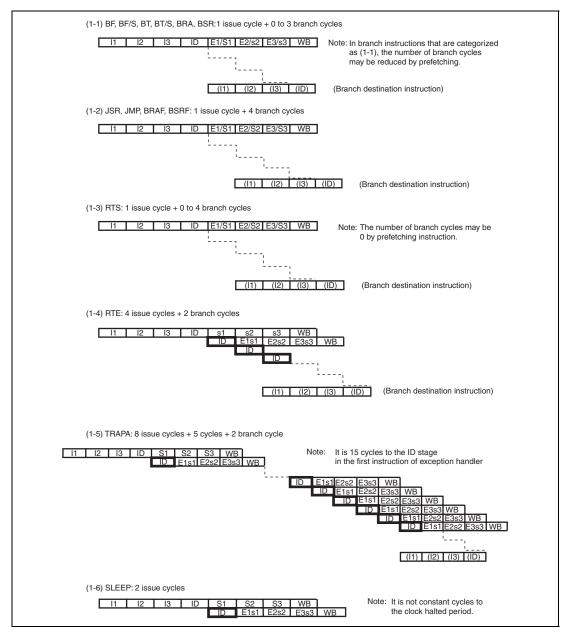

| 4.3  | Issue Rates and Execution Cycles     | 85 |

| Sect | tion 5 Exception Handling            | 95 |

| 5.1  | Summary of Exception Handling        | 95 |

| 5.2  | Register Descriptions                | 95 |

|      | 5.2.1 TRAPA Exception Register (TRA) | 96 |

|      | 5.2.2  | Exception Event Register (EXPEVT)                              | 97  |

|------|--------|----------------------------------------------------------------|-----|

|      | 5.2.3  | Interrupt Event Register (INTEVT)                              | 98  |

|      | 5.2.4  | Non-Support Detection Exception Register (EXPMASK)             | 99  |

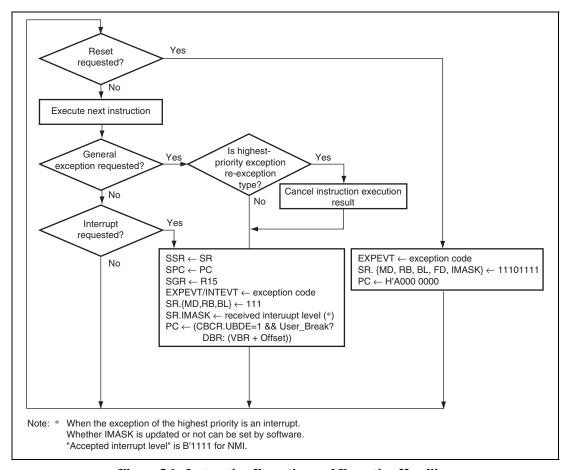

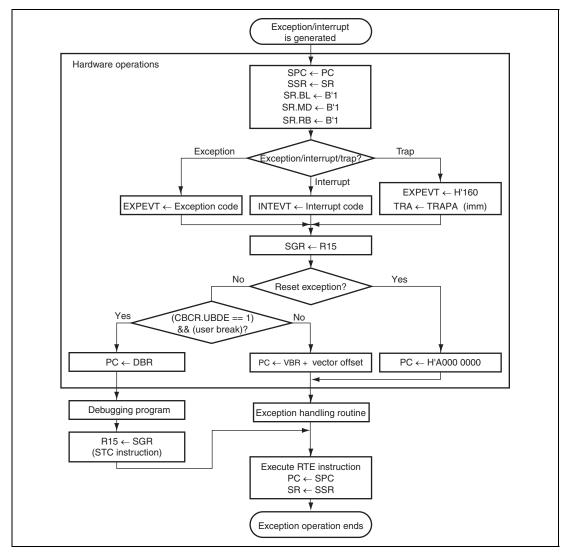

| 5.3  | Excep  | tion Handling Functions                                        | 101 |

|      | 5.3.1  | Exception Handling Flow                                        | 101 |

|      | 5.3.2  | Exception Handling Vector Addresses                            | 101 |

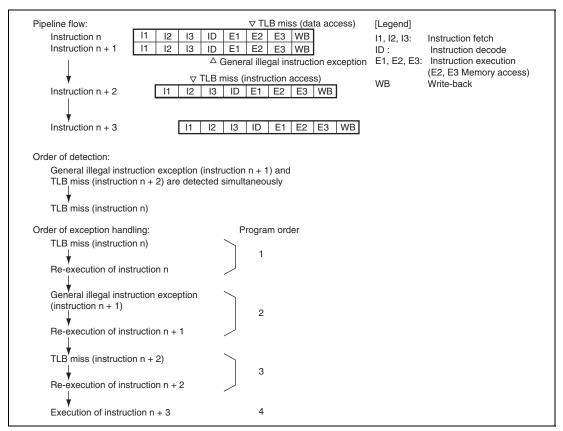

| 5.4  | Excep  | tion Types and Priorities                                      | 102 |

| 5.5  | Excep  | tion Flow                                                      | 104 |

|      | 5.5.1  | Exception Flow                                                 | 104 |

|      | 5.5.2  | Exception Source Acceptance                                    | 106 |

|      | 5.5.3  | Exception Requests and BL Bit                                  | 107 |

|      | 5.5.4  | Return from Exception Handling                                 | 107 |

| 5.6  | Descr  | iption of Exceptions                                           | 108 |

|      | 5.6.1  | Resets                                                         | 108 |

|      | 5.6.2  | General Exceptions                                             | 110 |

|      | 5.6.3  | Interrupts                                                     | 126 |

|      | 5.6.4  | Priority Order with Multiple Exceptions                        | 127 |

| 5.7  | Usage  | Notes                                                          | 129 |

| Sect | tion 6 | Floating-Point Unit (FPU)                                      | 131 |

| 6.1  |        | es                                                             |     |

| 6.2  |        | Formats                                                        |     |

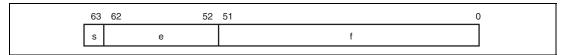

|      | 6.2.1  | Floating-Point Format                                          |     |

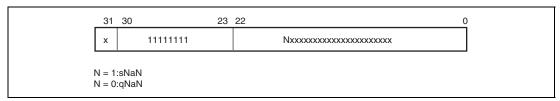

|      | 6.2.2  | Non-Numbers (NaN)                                              |     |

|      | 6.2.3  | Denormalized Numbers                                           |     |

| 6.3  | Regist | ter Descriptions                                               |     |

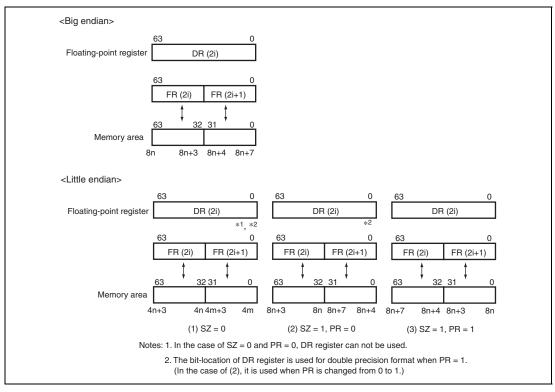

|      | 6.3.1  | Floating-Point Registers                                       |     |

|      | 6.3.2  | Floating-Point Status/Control Register (FPSCR)                 |     |

|      | 6.3.3  | Floating-Point Communication Register (FPUL)                   |     |

| 6.4  | Round  | ling                                                           |     |

| 6.5  |        | ng-Point Exceptions                                            |     |

|      | 6.5.1  | General FPU Disable Exceptions and Slot FPU Disable Exceptions |     |

|      | 6.5.2  | FPU Exception Sources                                          |     |

|      | 6.5.3  | FPU Exception Handling                                         |     |

| 6.6  | Graph  | ics Support Functions                                          |     |

|      | 6.6.1  | Geometric Operation Instructions                               |     |

|      | 6.6.2  | Pair Single-Precision Data Transfer                            |     |

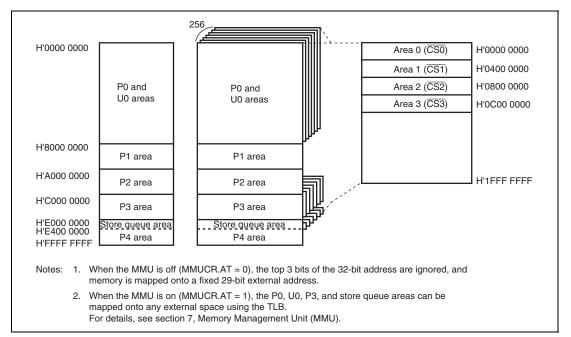

| Sect | tion 7 | Memory Management Unit (MMU)                                   | 149 |

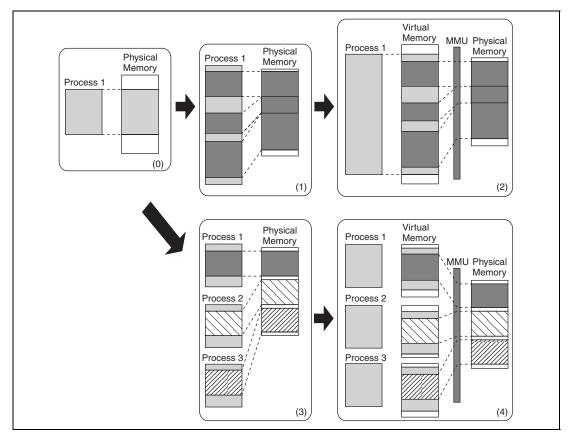

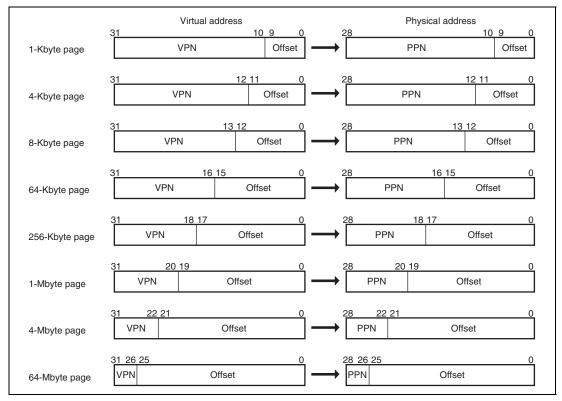

| 7 1  |        | iew of MMI                                                     | 150 |

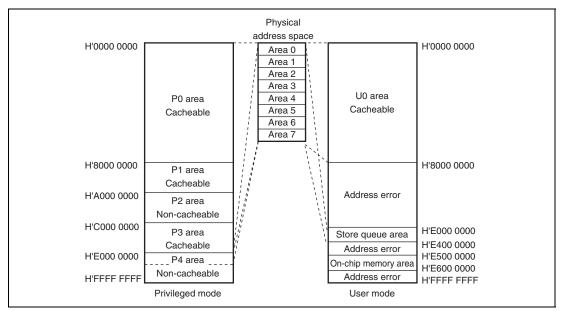

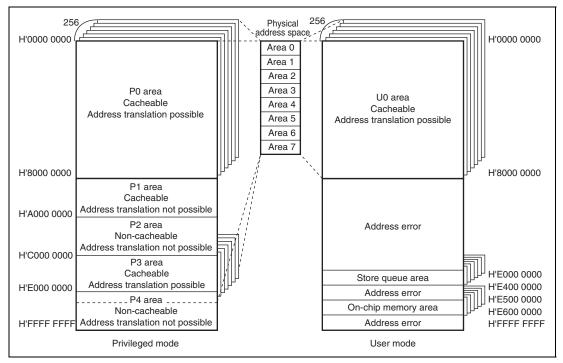

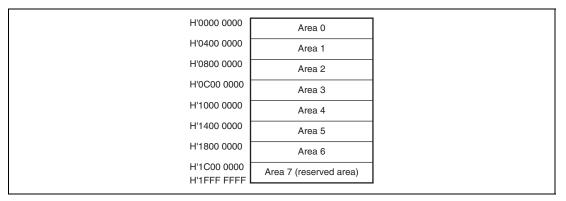

|     | 7.1.1  | Address Spaces                                        | 152 |

|-----|--------|-------------------------------------------------------|-----|

| 7.2 | Regist | ter Descriptions                                      | 158 |

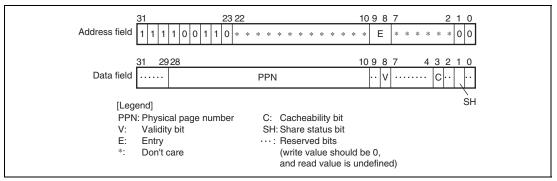

|     | 7.2.1  | Page Table Entry High Register (PTEH)                 | 159 |

|     | 7.2.2  | Page Table Entry Low Register (PTEL)                  | 160 |

|     | 7.2.3  | Translation Table Base Register (TTB)                 |     |

|     | 7.2.4  | TLB Exception Address Register (TEA)                  | 162 |

|     | 7.2.5  | MMU Control Register (MMUCR)                          | 162 |

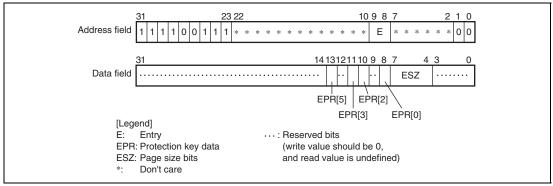

|     | 7.2.6  | Page Table Entry Assistance Register (PTEA)           | 166 |

|     | 7.2.7  | Physical Address Space Control Register (PASCR)       | 167 |

|     | 7.2.8  | Instruction Re-Fetch Inhibit Control Register (IRMCR) | 168 |

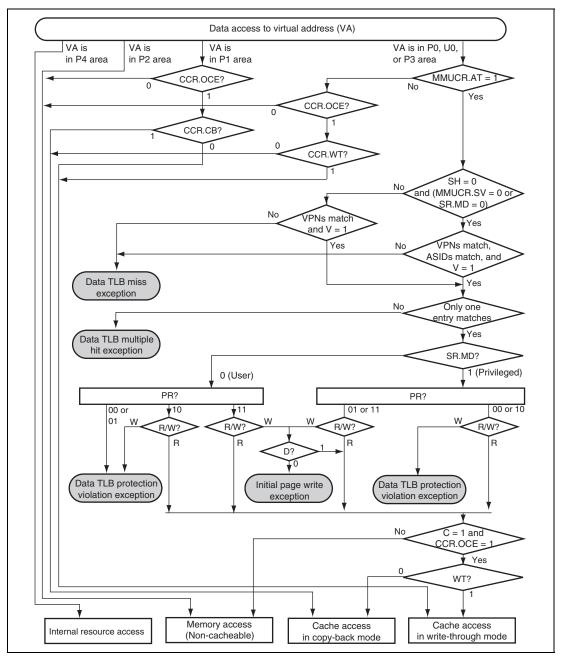

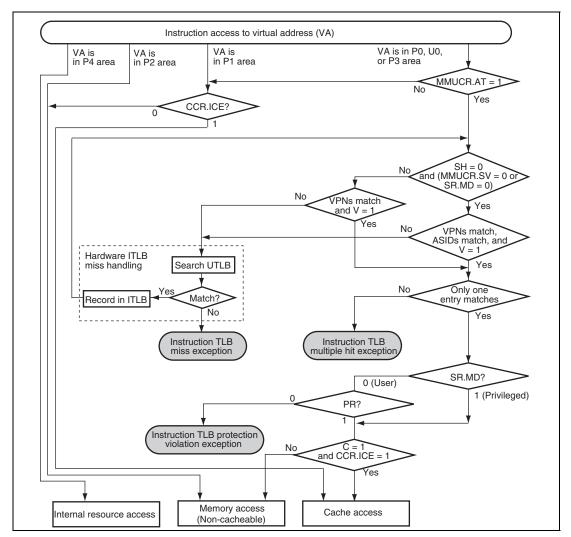

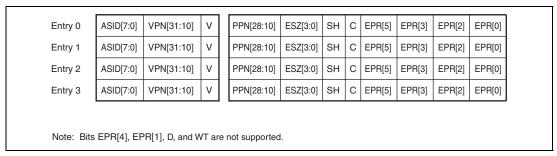

| 7.3 | TLB F  | Functions (TLB Compatible Mode; MMUCR.ME = 0)         | 170 |

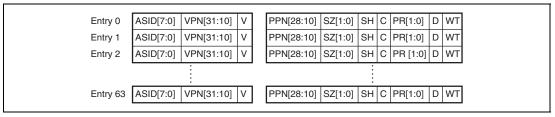

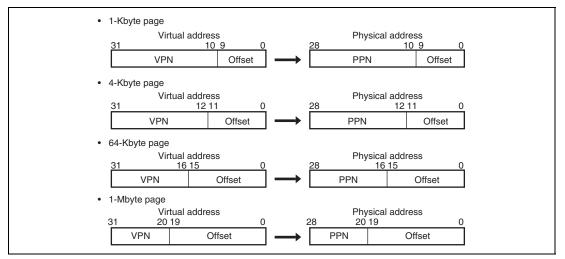

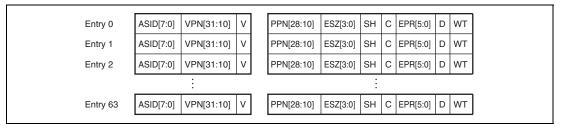

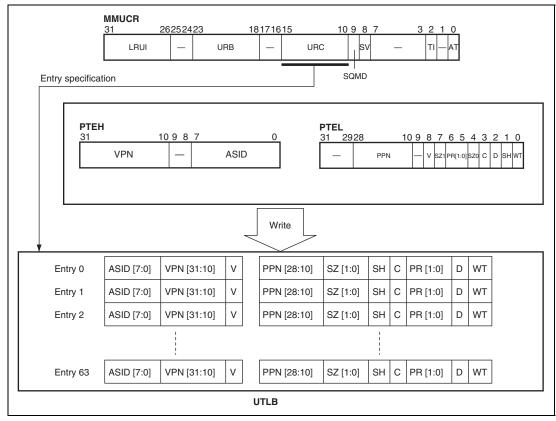

|     | 7.3.1  | Unified TLB (UTLB) Configuration                      | 170 |

|     | 7.3.2  | Instruction TLB (ITLB) Configuration                  | 173 |

|     | 7.3.3  | Address Translation Method                            | 173 |

| 7.4 | TLB F  | Functions (TLB Extended Mode; MMUCR.ME = 1)           | 176 |

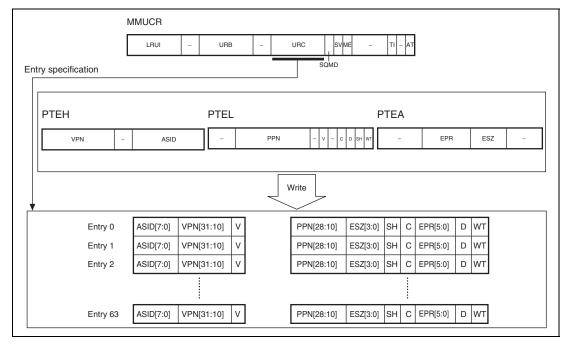

|     | 7.4.1  | Unified TLB (UTLB) Configuration                      | 176 |

|     | 7.4.2  | Instruction TLB (ITLB) Configuration                  |     |

|     | 7.4.3  | Address Translation Method                            | 180 |

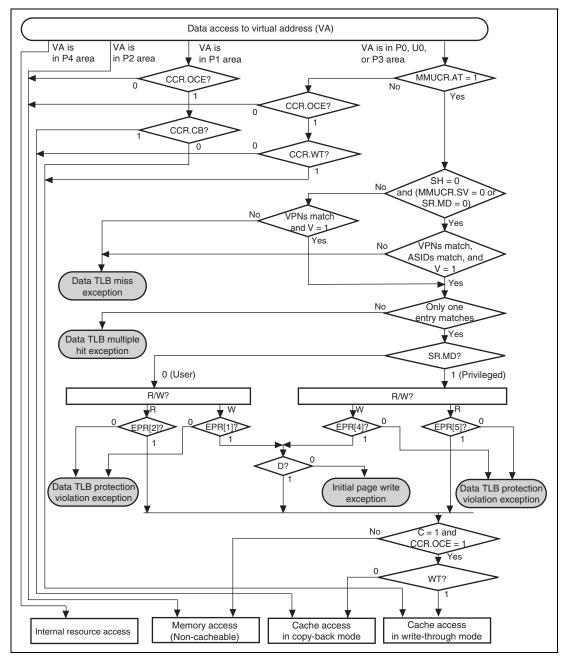

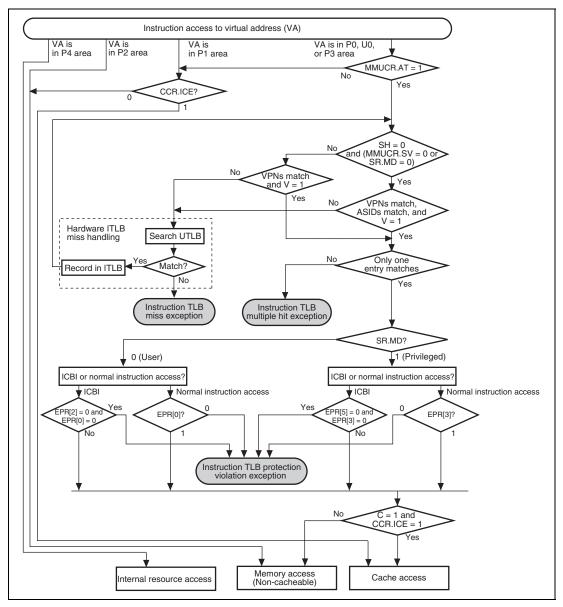

| 7.5 | MMU    | Functions                                             | 183 |

|     | 7.5.1  | MMU Hardware Management                               | 183 |

|     | 7.5.2  | MMU Software Management                               | 183 |

|     | 7.5.3  | MMU Instruction (LDTLB)                               |     |

|     | 7.5.4  | Hardware ITLB Miss Handling                           | 186 |

|     | 7.5.5  | Avoiding Synonym Problems                             | 187 |

| 7.6 | MMU    | Exceptions                                            |     |

|     | 7.6.1  | Instruction TLB Multiple Hit Exception                |     |

|     | 7.6.2  | Instruction TLB Miss Exception                        |     |

|     | 7.6.3  | Instruction TLB Protection Violation Exception        |     |

|     | 7.6.4  | Data TLB Multiple Hit Exception                       | 192 |

|     | 7.6.5  | Data TLB Miss Exception                               |     |

|     | 7.6.6  | Data TLB Protection Violation Exception               |     |

|     | 7.6.7  | Initial Page Write Exception                          |     |

| 7.7 | Memo   | ory-Mapped TLB Configuration                          |     |

|     | 7.7.1  | ITLB Address Array                                    |     |

|     | 7.7.2  | ITLB Data Array (TLB Compatible Mode)                 |     |

|     | 7.7.3  | ITLB Data Array (TLB Extended Mode)                   |     |

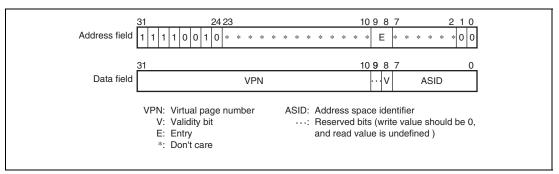

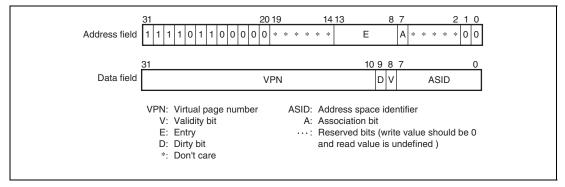

|     | 7.7.4  | UTLB Address Array                                    |     |

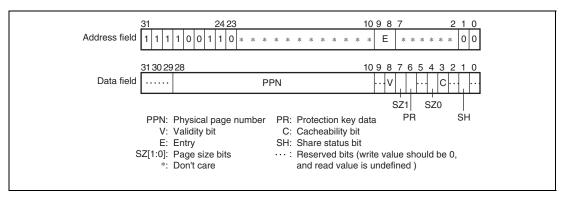

|     | 7.7.5  | UTLB Data Array (TLB Compatible Mode)                 |     |

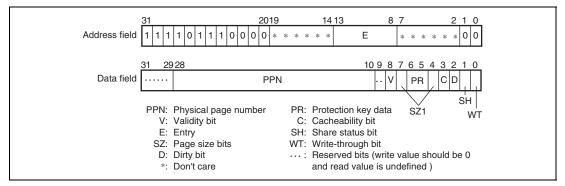

|     | 7.7.6  | UTLB Data Array (TLB Extended Mode)                   |     |

| 7.8 | Usage  | Notes                                                 | 206 |

|      | 7.8.1                             | Note on Using LDTLB Instruction                 | 206 |

|------|-----------------------------------|-------------------------------------------------|-----|

| Sect | tion 8                            | Caches                                          | 207 |

| 8.1  | Featu                             | ıres                                            | 207 |

| 8.2  |                                   | ster Descriptions                               |     |

|      | 8.2.1                             | Cache Control Register (CCR)                    |     |

|      | 8.2.2                             |                                                 |     |

|      | 8.2.3                             |                                                 |     |

|      | 8.2.4                             |                                                 |     |

| 8.3  | Opera                             | and Cache Operation                             |     |

|      | 8.3.1                             | Read Operation                                  |     |

|      | 8.3.2                             | Prefetch Operation                              | 219 |

|      | 8.3.3                             | Write Operation                                 | 220 |

|      | 8.3.4                             | Write-Back Buffer                               | 221 |

|      | 8.3.5                             | Write-Through Buffer                            | 221 |

|      | 8.3.6                             | OC Two-Way Mode                                 | 222 |

| 8.4  | Instru                            | action Cache Operation                          |     |

|      | 8.4.1                             | Read Operation                                  | 223 |

|      | 8.4.2                             | Prefetch Operation                              | 223 |

|      | 8.4.3                             | IC Two-Way Mode                                 | 224 |

|      | 8.4.4                             | Instruction Cache Way Prediction Operation      | 224 |

| 8.5  | Cach                              | e Operation Instruction                         | 225 |

|      | 8.5.1                             | Coherency between Cache and External Memory     | 225 |

|      | 8.5.2                             | Prefetch Operation                              | 227 |

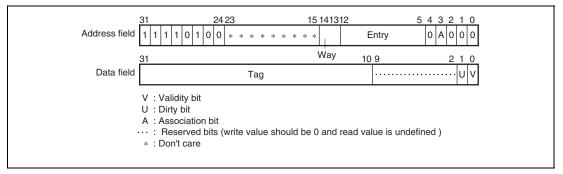

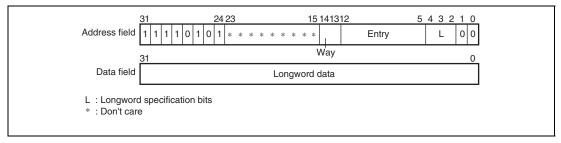

| 8.6  | Memory-Mapped Cache Configuration |                                                 | 228 |

|      | 8.6.1                             | IC Address Array                                | 228 |

|      | 8.6.2                             | IC Data Array                                   | 230 |

|      | 8.6.3                             | OC Address Array                                | 230 |

|      | 8.6.4                             | OC Data Array                                   | 232 |

|      | 8.6.5                             | Memory-Mapped Cache Associative Write Operation | 233 |

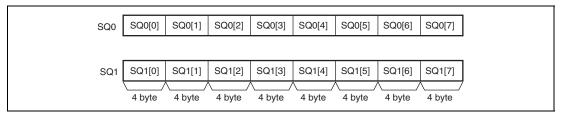

| 8.7  | Store                             | Queues                                          | 234 |

|      | 8.7.1                             | SQ Configuration                                | 234 |

|      | 8.7.2                             | Writing to SQ                                   | 234 |

|      | 8.7.3                             | Transfer to External Memory                     | 235 |

|      | 8.7.4                             | Determination of SQ Access Exception            | 236 |

|      | 8.7.5                             | Reading from SQ                                 | 236 |

| Sect | tion 9                            | On-Chip Memory                                  | 237 |

| 9.1  |                                   | ires                                            |     |

| 92   | Regis                             | eter Descriptions                               | 238 |

|      | 9.2.1   | On-Chip Memory Control Register (RAMCR)                                | 239 |

|------|---------|------------------------------------------------------------------------|-----|

| 9.3  | Operat  | ion                                                                    | 241 |

|      | 9.3.1   | Instruction Fetch Access from the CPU                                  | 241 |

|      | 9.3.2   | Operand Access from the CPU and Access from the FPU                    | 241 |

|      | 9.3.3   | Access from the SuperHyway Bus Master Module                           | 241 |

| 9.4  | On-Ch   | ip Memory Protective Functions                                         | 242 |

| 9.5  | Usage   | Notes                                                                  | 243 |

|      | 9.5.1   | Page Conflict                                                          | 243 |

|      | 9.5.2   | Access Across Different Pages                                          | 243 |

|      | 9.5.3   | On-Chip Memory Coherency                                               | 243 |

|      | 9.5.4   | Sleep Mode                                                             | 243 |

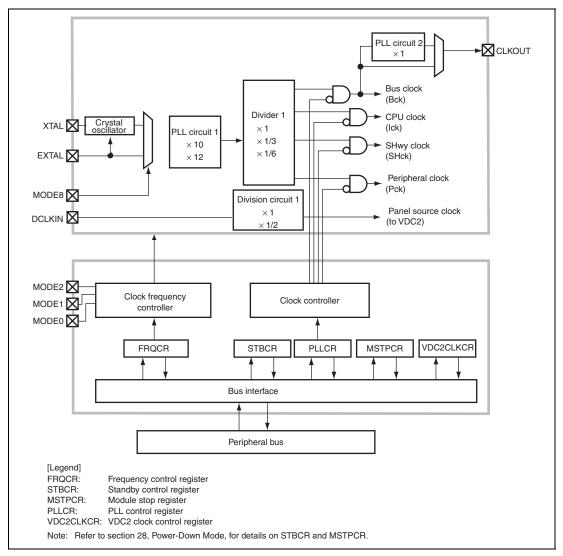

| Sect | ion 10  | Clock Pulse Generator (CPG)                                            | 245 |

| 10.1 | Feature | es                                                                     | 245 |

| 10.2 | Input/0 | Output Pins                                                            | 248 |

| 10.3 | Clock   | Operating Mode                                                         | 249 |

| 10.4 | Registe | er Descriptions                                                        | 250 |

|      | 10.4.1  | Frequency Control Register (FRQCR)                                     | 251 |

|      | 10.4.2  | PLL Control Register (PLLCR)                                           | 253 |

|      | 10.4.3  | VDC2 Clock Control Register (VDC2CLKCR)                                | 254 |

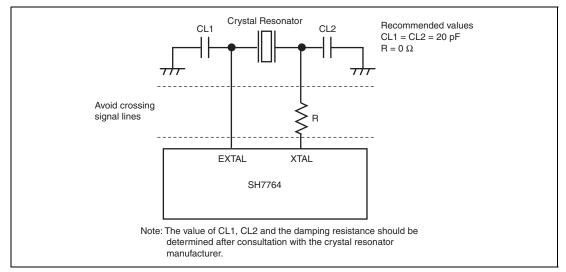

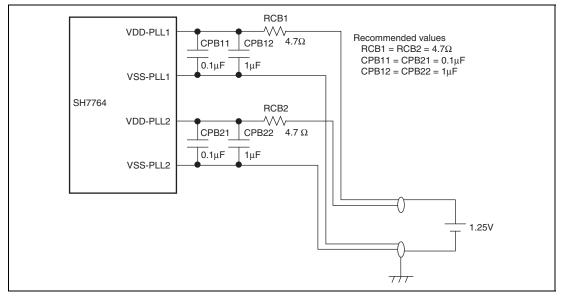

| 10.5 | Notes   | on Board Design                                                        | 255 |

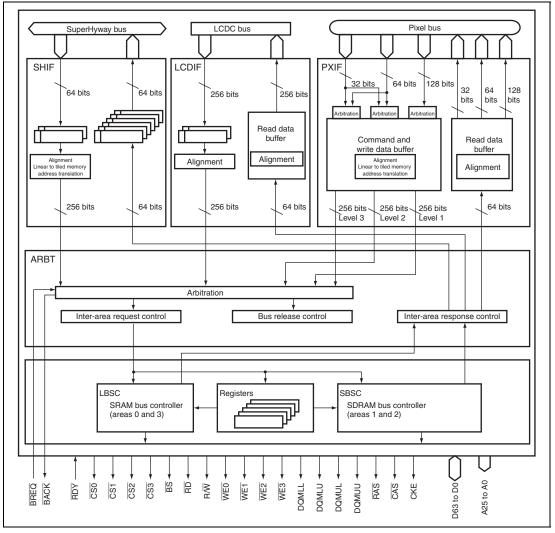

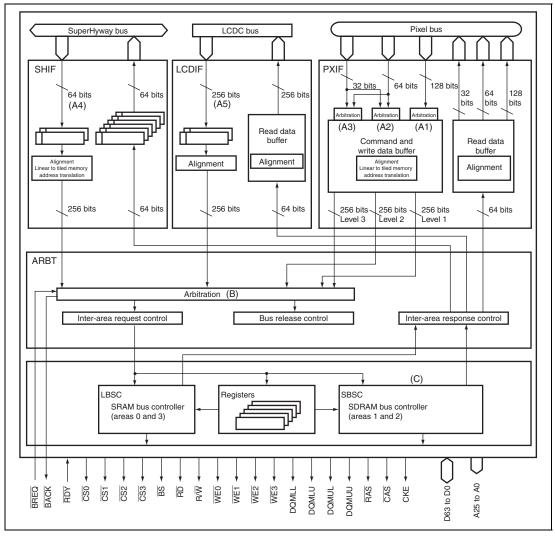

| Sect | ion 11  | Memory Controller Unit (MCU)                                           | 257 |

| 11.1 | Feature | es                                                                     | 257 |

| 11.2 | Input/0 | Output Pins                                                            | 260 |

| 11.3 | Area C  | Overview                                                               | 262 |

|      | 11.3.1  | Space Divisions                                                        | 262 |

|      | 11.3.2  | Memory Bus Width                                                       | 263 |

|      | 11.3.3  | Endian Setting                                                         | 264 |

| 11.4 | Registe | er Description                                                         | 265 |

|      | 11.4.1  | Version Control Register (VCR)                                         | 268 |

|      | 11.4.2  |                                                                        |     |

|      | 11.4.3  | SDRAM Control Register (SCR)                                           | 273 |

|      | 11.4.4  | 6 6 . ,                                                                |     |

|      | 11.4.5  | SDRAM Row Attribute Register (SDRA)                                    | 278 |

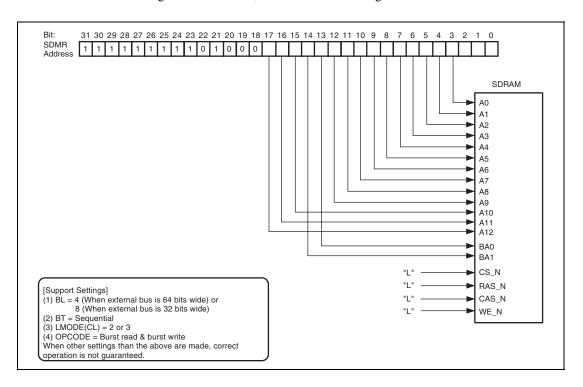

|      | 11.4.6  | SDRAM Mode Register (SDMR)                                             | 280 |

|      | 11.4.7  | Arbitration Mode Register (AMR)                                        | 281 |

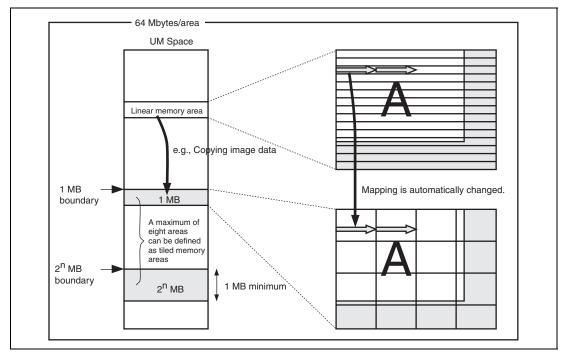

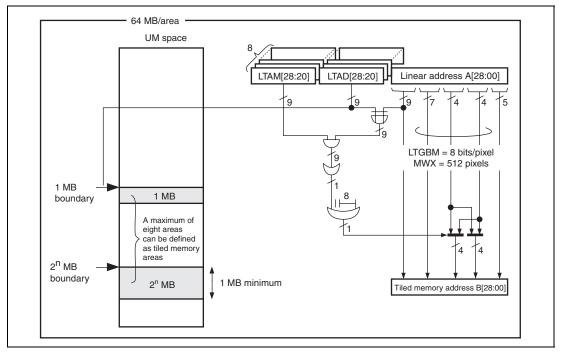

|      | 11.4.8  | Linear-to-Tiled Memory Address Translation Control Register (LTCn)     | 282 |

|      | 11.4.9  | Linear-to-Tiled Memory Address Translation Area Start Address Register |     |

|      |         | (LTADn)                                                                | 284 |

|       | 11.4.10 | Linear-to-Tiled Memory Address Translation Area  |     |

|-------|---------|--------------------------------------------------|-----|

|       |         | Start Address Mask Register (LTAMn)              | 285 |

|       | 11.4.11 | Request Mask Setting Register (RQM)              | 286 |

|       | 11.4.12 | 2 Bus Control Register (BCR)                     | 289 |

|       | 11.4.13 | 3 CS0 Bus Control Register (CS0BCR)              | 292 |

|       | 11.4.14 | 4 CSn Wait Control Register (CSnWCR)             | 297 |

|       | 11.4.15 | 5 CS3 Bus Control Register (CS3BCR)              | 303 |

| 11.5  | Operat  | ion                                              | 309 |

|       | 11.5.1  | Endian/Access Size and Data Alignment            | 309 |

|       | 11.5.2  | Data Alignment in Various Modules                | 318 |

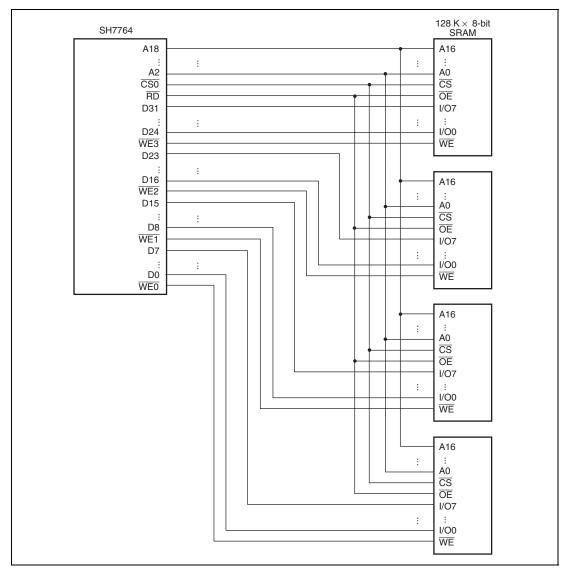

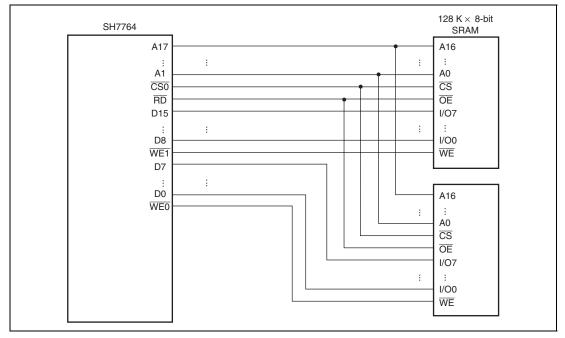

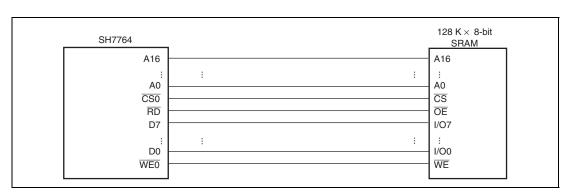

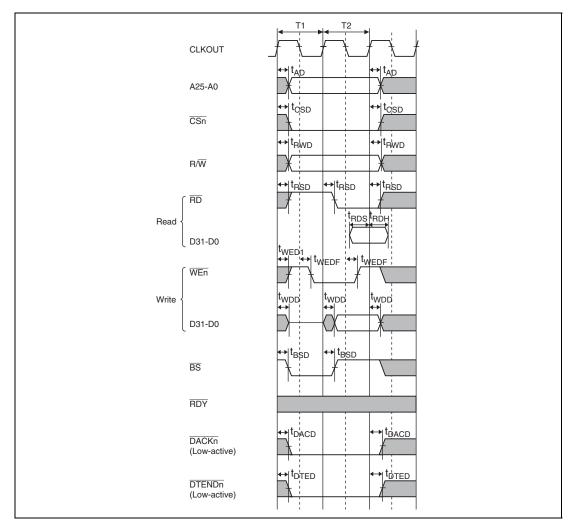

| 11.6  | SRAM    | Interface                                        | 318 |

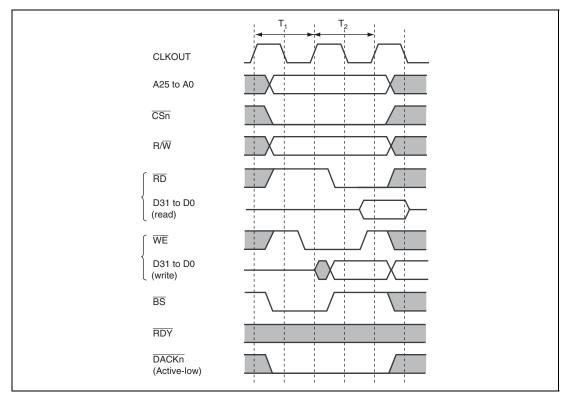

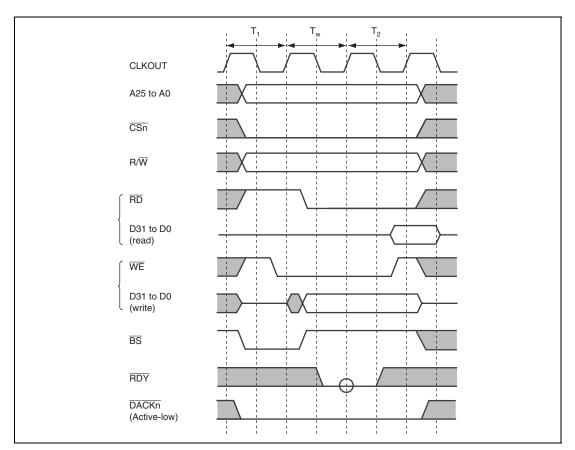

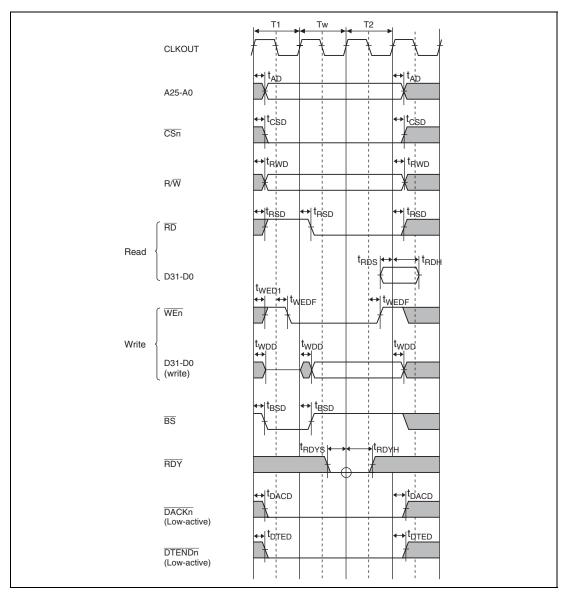

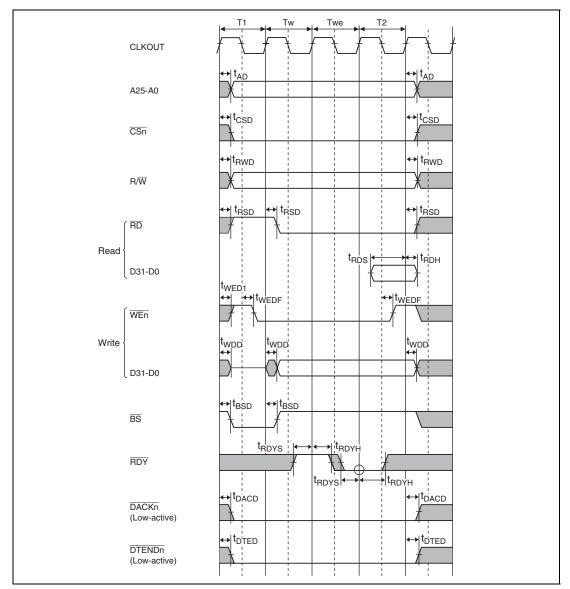

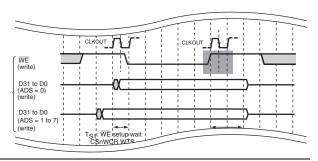

|       | 11.6.1  | Basic Timing                                     | 318 |

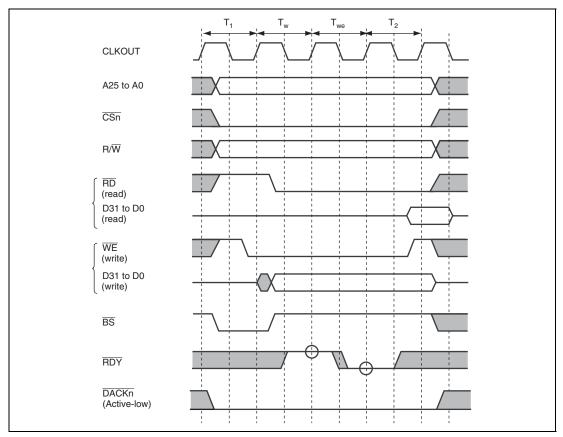

|       | 11.6.2  | Wait Cycle Control                               | 322 |

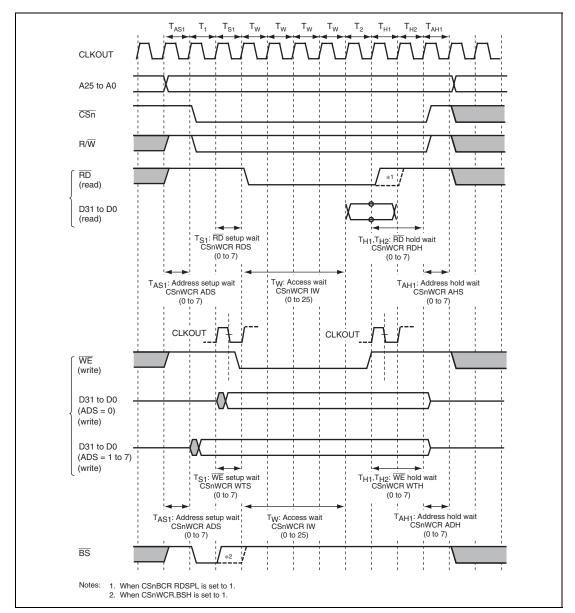

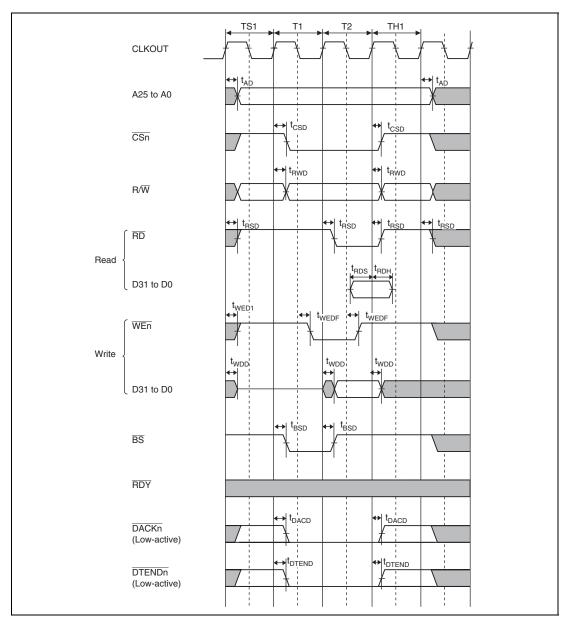

|       | 11.6.3  | Read-Strobe Negate Timing                        | 324 |

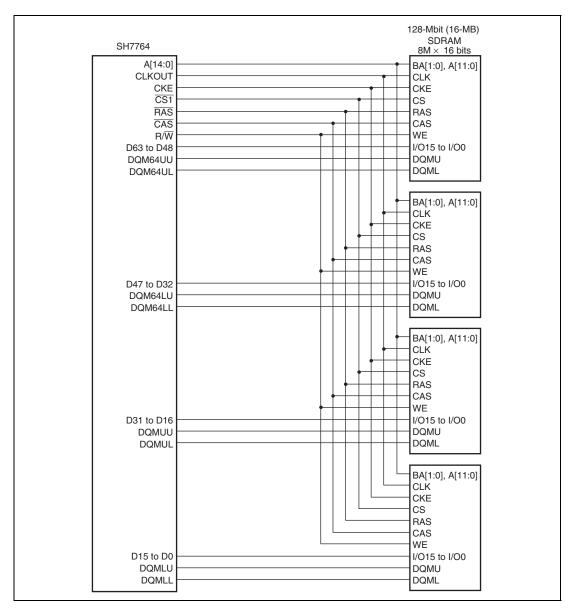

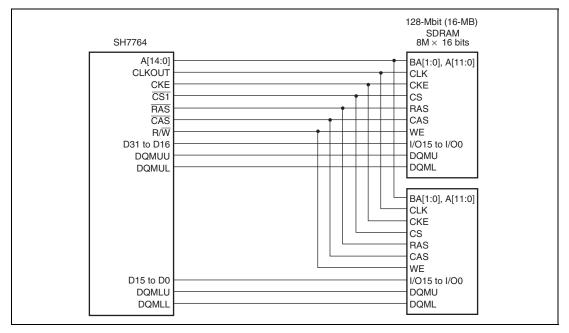

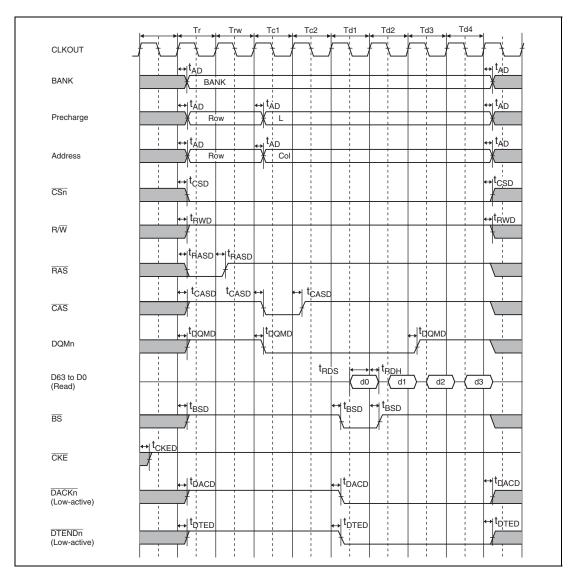

| 11.7  | SDRA    | M Interface                                      | 325 |

|       | 11.7.1  | SDRAM Direct Connection                          | 325 |

|       | 11.7.2  | Address Multiplexing                             | 328 |

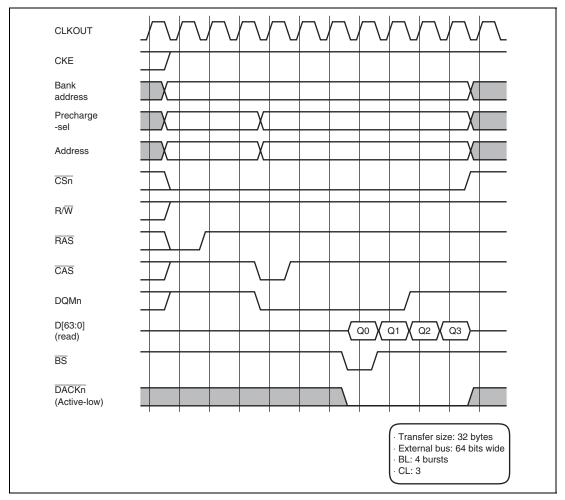

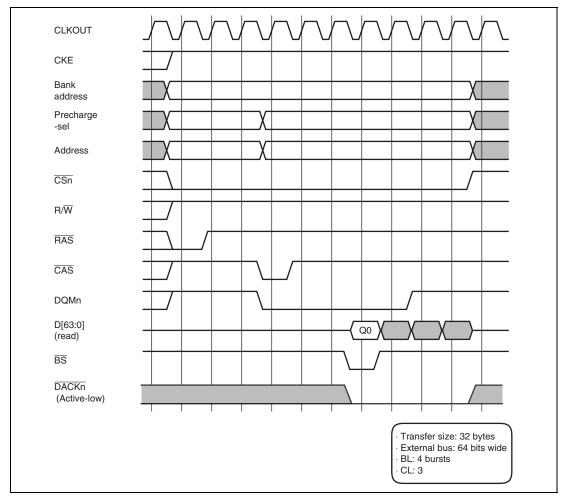

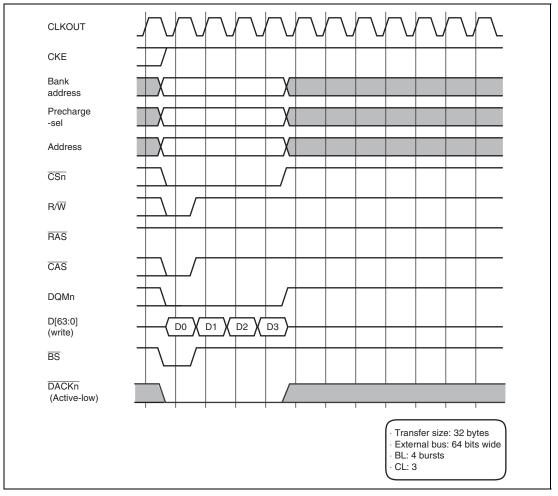

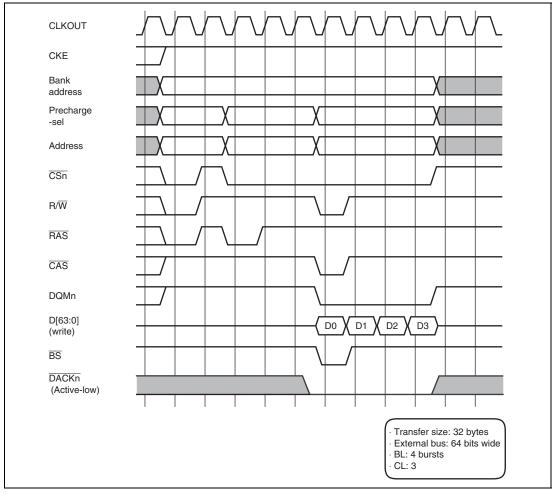

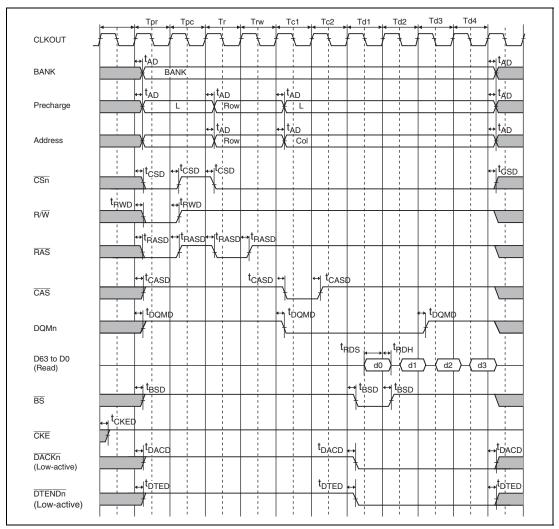

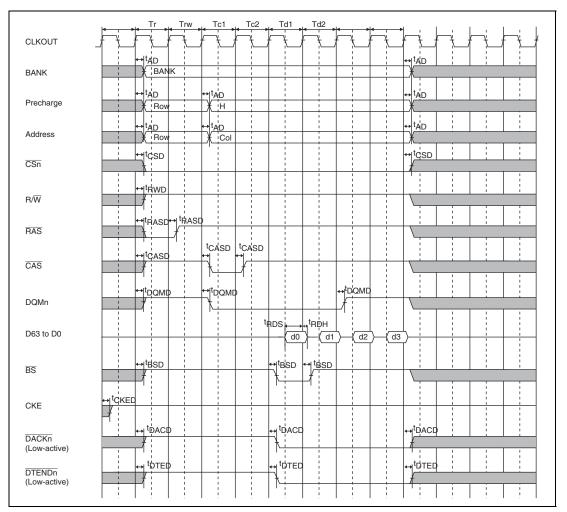

|       | 11.7.3  | Burst Read                                       | 330 |

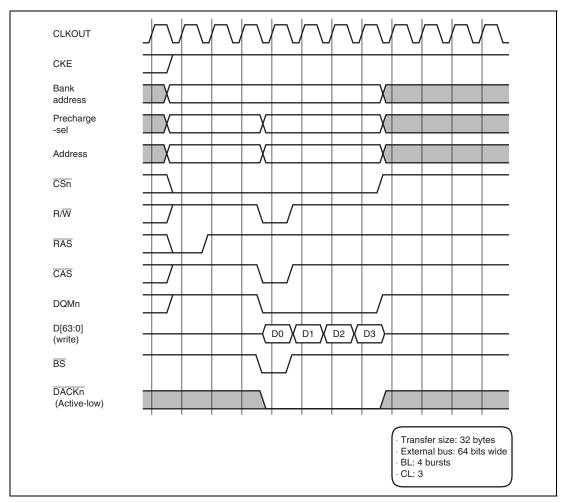

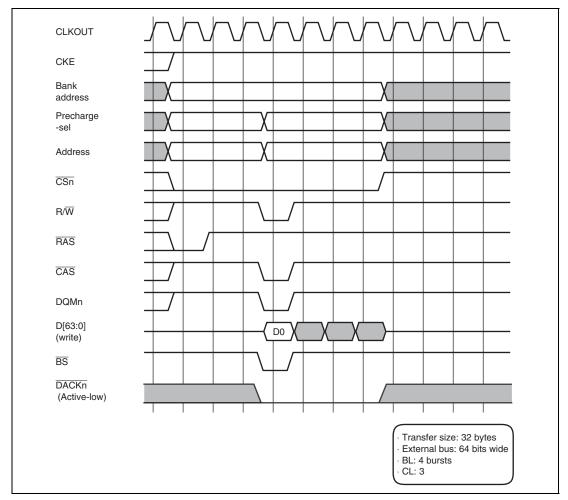

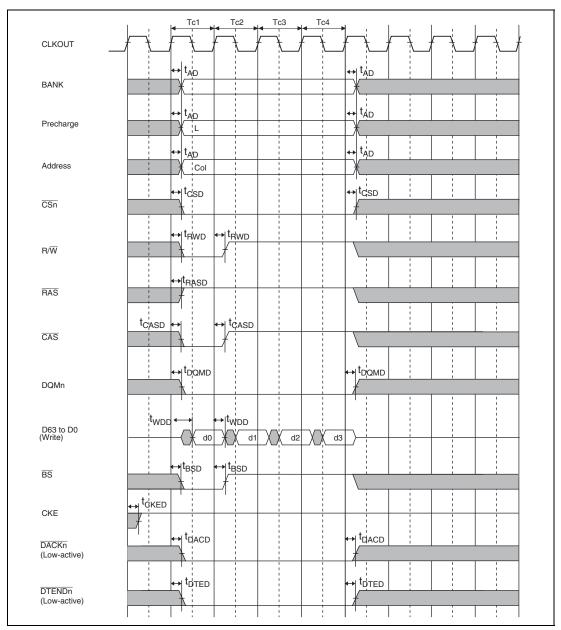

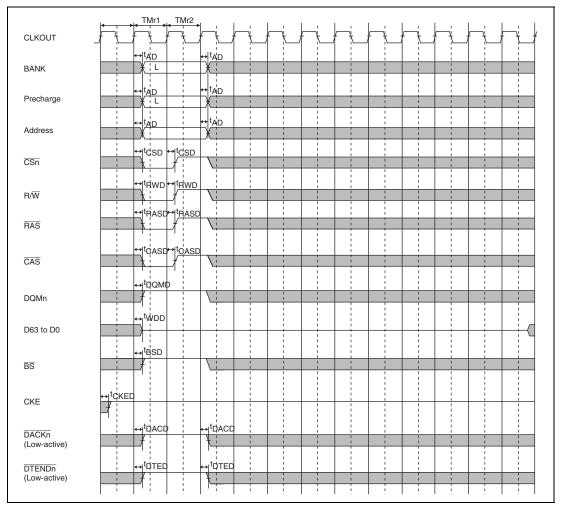

|       | 11.7.4  | Burst Write                                      | 331 |

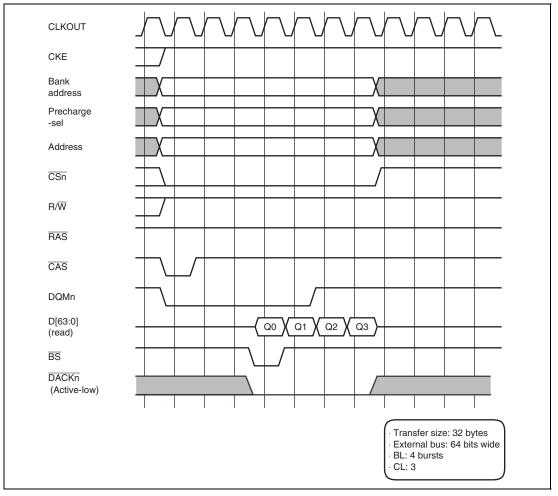

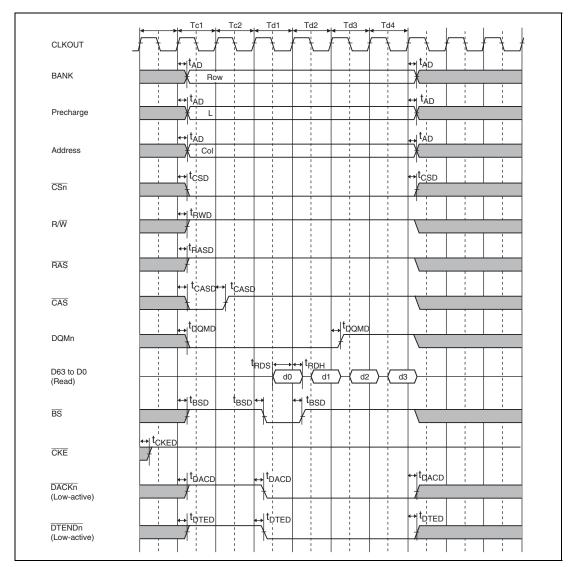

|       | 11.7.5  | Single Read                                      | 332 |

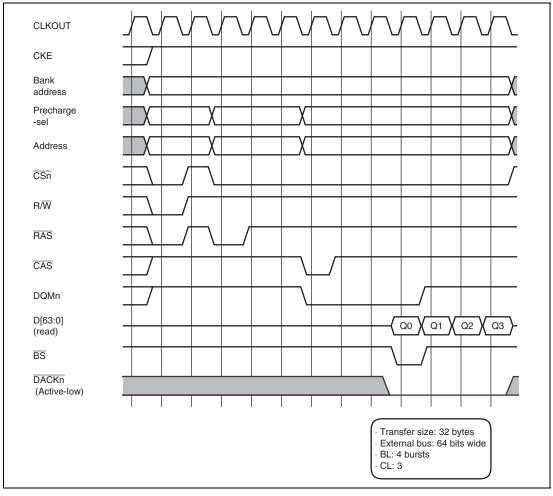

|       | 11.7.6  | Single Write                                     | 333 |

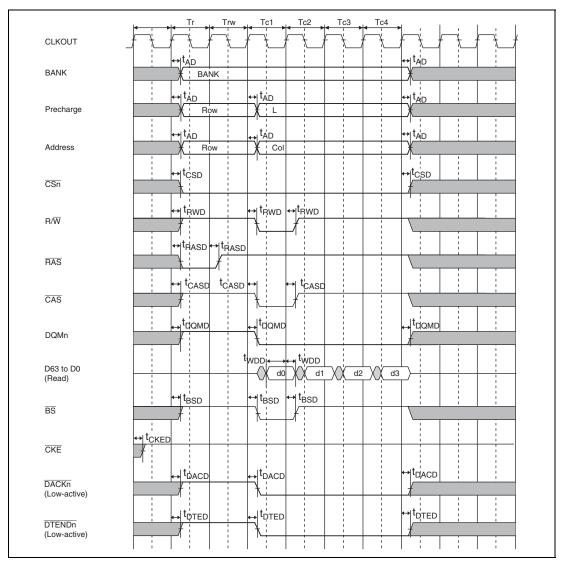

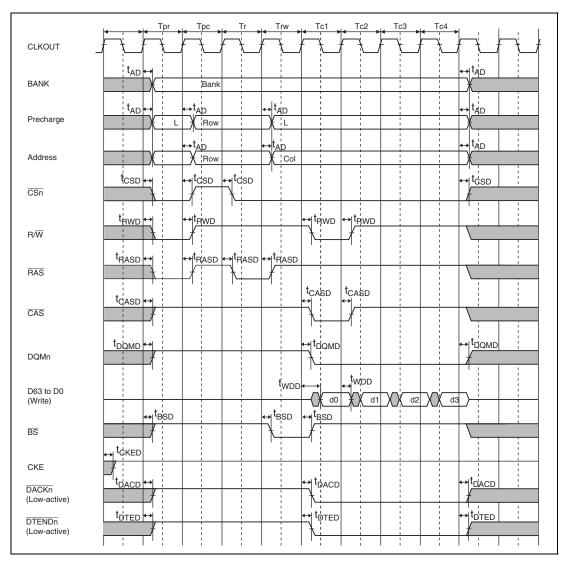

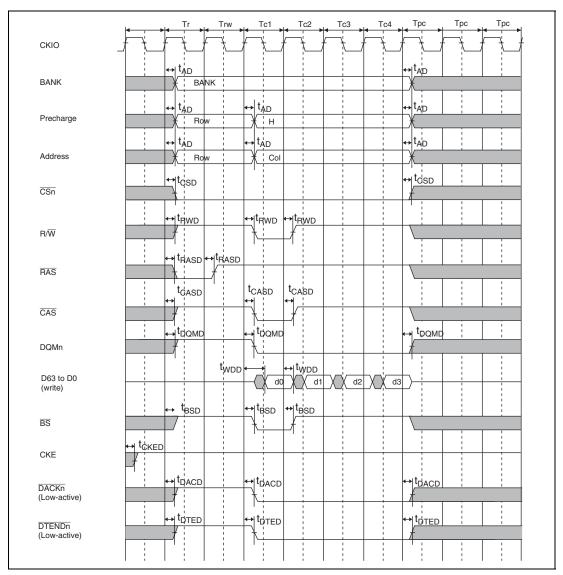

|       | 11.7.7  | Bank Open Mode                                   | 334 |

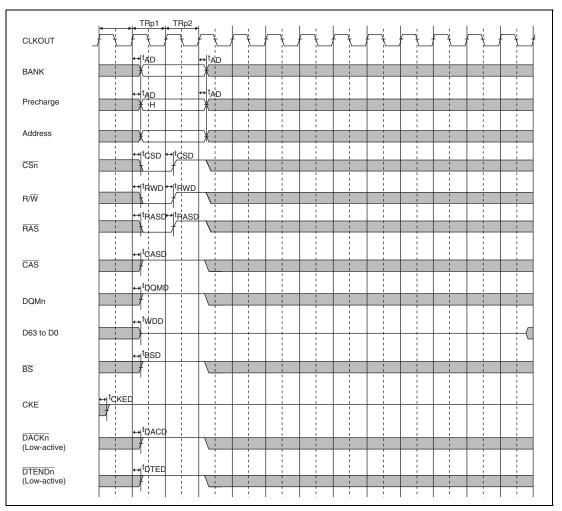

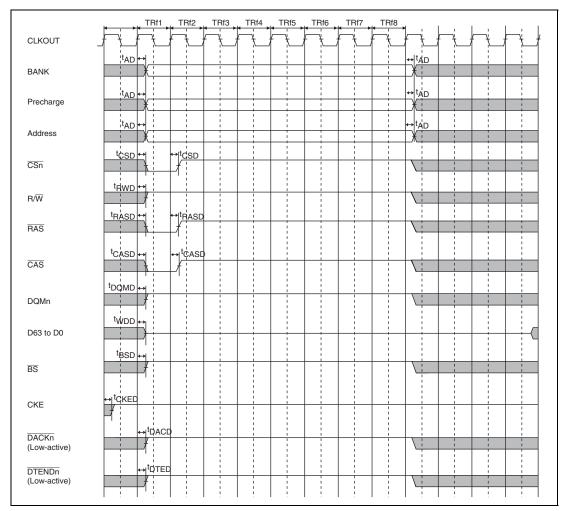

|       | 11.7.8  | Refresh                                          | 339 |

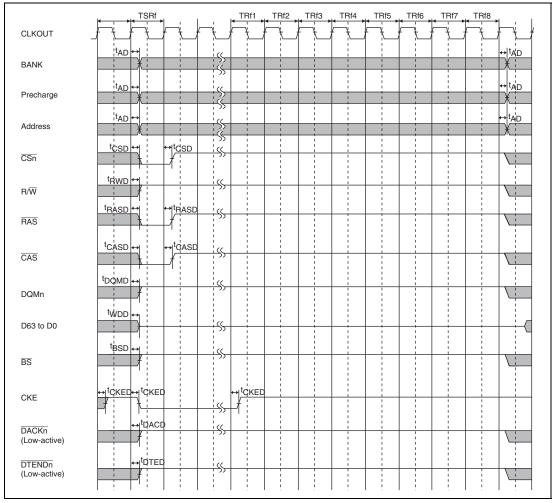

|       | 11.7.9  | SDRAM Initialization Sequence                    | 340 |

| 11.8  | Wait C  | ycles between Accesses                           | 341 |

|       | 11.8.1  | Wait Cycles between Accesses to Area 0 or 3      | 341 |

|       | 11.8.2  | Wait Cycles between Accesses to Area 1 or 2      | 341 |

|       | 11.8.3  | Wait Cycles between Access to Area 1 or 2        |     |

|       |         | and the Subsequent Access to Area 0 or 3         | 341 |

| 11.9  | Bus Ar  | bitration                                        | 342 |

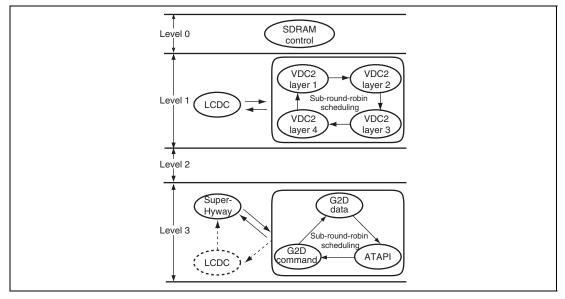

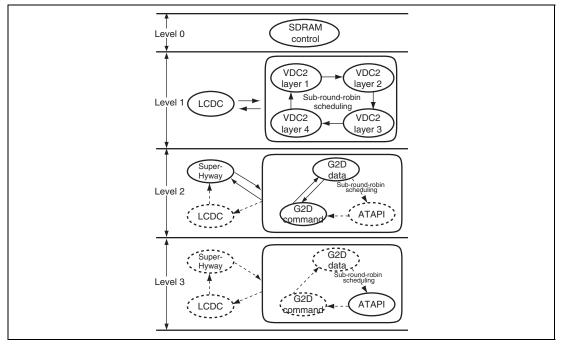

|       | 11.9.1  | Arbitration of Accesses between Internal Modules | 342 |

|       | 11.9.2  | Multi-Step Arbitration                           | 345 |

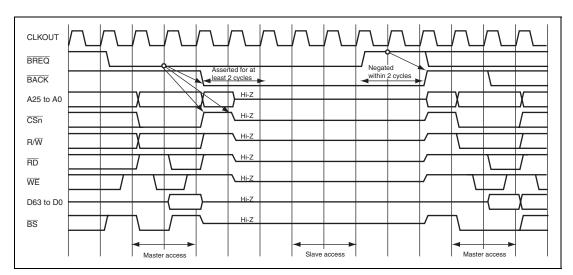

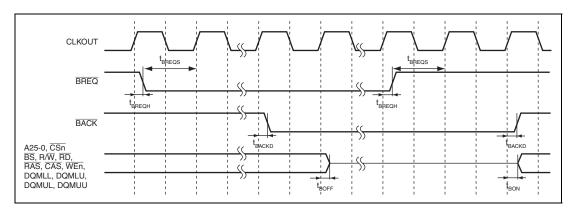

|       | 11.9.3  | Bus Requests from External Devices               | 348 |

|       |         | Bus Release and Recovery Sequences               |     |

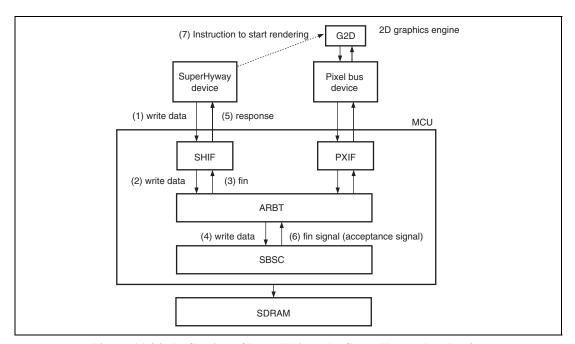

|       | 11.9.5  | Cooperation between Master and Slave             | 351 |

| 11.10 | Data C  | oherency                                         | 351 |

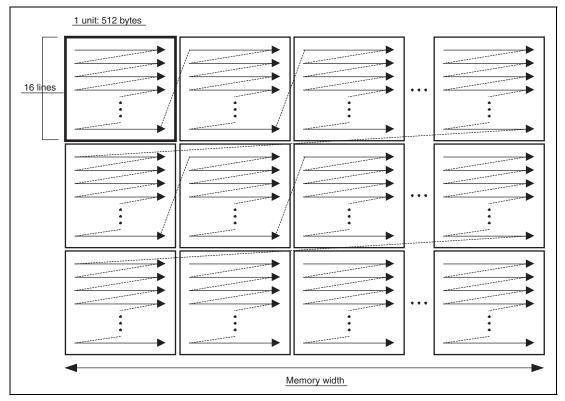

|       |         | to-Tiled Memory Address Translation              |     |

|       |         | Notes                                            |     |

|       | 11.12.1 | Refresh                                          | 359 |

|       |         | External Dua Arbitration                         |     |

|          | 11.12.3 | B Pixel Bus Transfer Size and Access Address Boundary               | 359 |

|----------|---------|---------------------------------------------------------------------|-----|

|          | 11.12.4 | Actions When Wait States are Not Inserted by RDY                    | 359 |

| <b>a</b> |         |                                                                     | 261 |

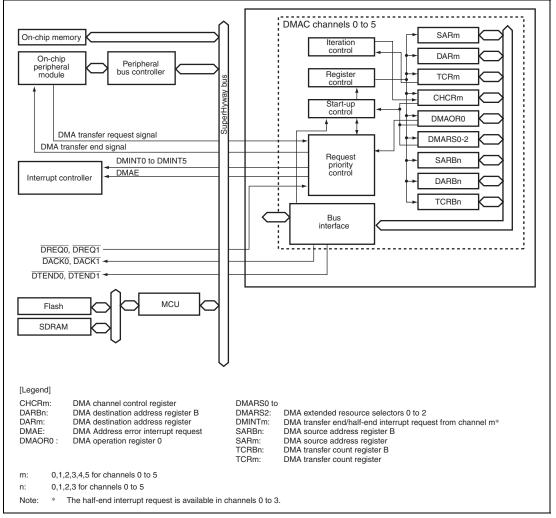

|          |         | Direct Memory Access Controller (DMAC)                              |     |

| 12.1     |         | 28                                                                  |     |

| 12.2     | -       | Output Pins                                                         |     |

| 12.3     |         | er Descriptions                                                     |     |

|          |         | DMA Source Address Registers (SAR0 to SAR5)                         |     |

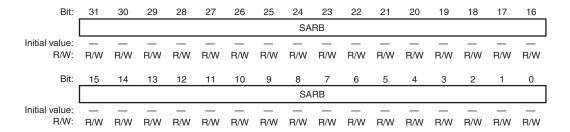

|          |         | DMA Source Address Registers (SARB0 to SARB3)                       |     |

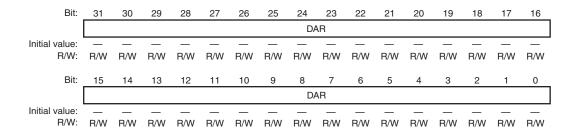

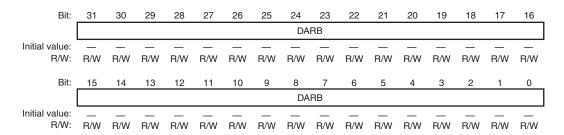

|          |         | DMA Destination Address Registers (DAR0 to DAR5)                    |     |

|          |         | DMA Destination Address Registers (DARB0 to DARB3)                  |     |

|          | 12.3.5  | DMA Transfer Count Registers (TCR0 to TCR5)                         | 370 |

|          | 12.3.6  | DMA Transfer Count Registers (TCRB0 to TCRB3)                       | 371 |

|          | 12.3.7  | DMA Channel Control Registers (CHCR0 to CHCR5)                      | 372 |

|          | 12.3.8  | DMA Operation Register 0 (DMAOR0)                                   | 380 |

|          | 12.3.9  | DMA Extended Resource Selectors (DMARS0 to DMARS2)                  | 383 |

| 12.4     | Operat  | ion                                                                 | 386 |

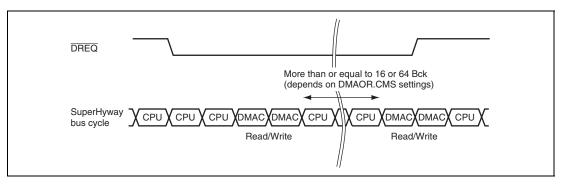

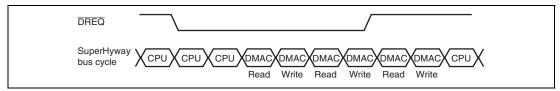

|          | 12.4.1  | DMA Transfer Requests                                               | 386 |

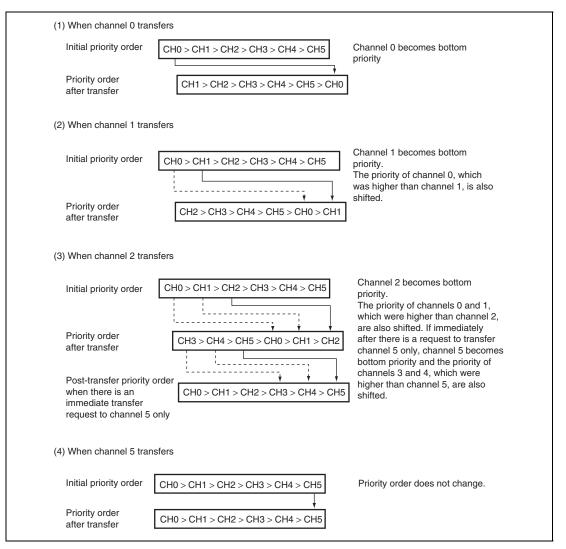

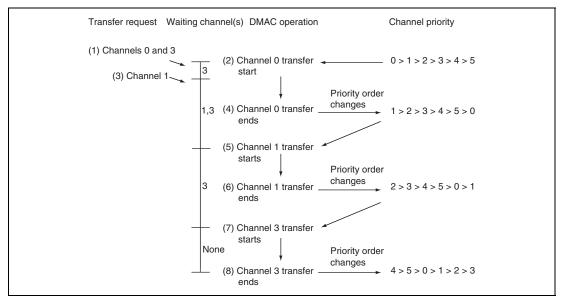

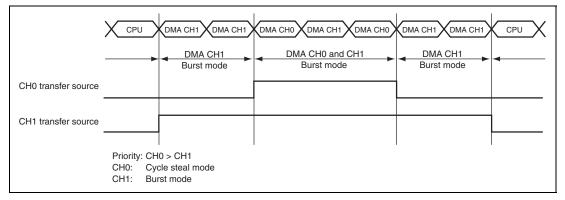

|          | 12.4.2  | Channel Priority                                                    | 390 |

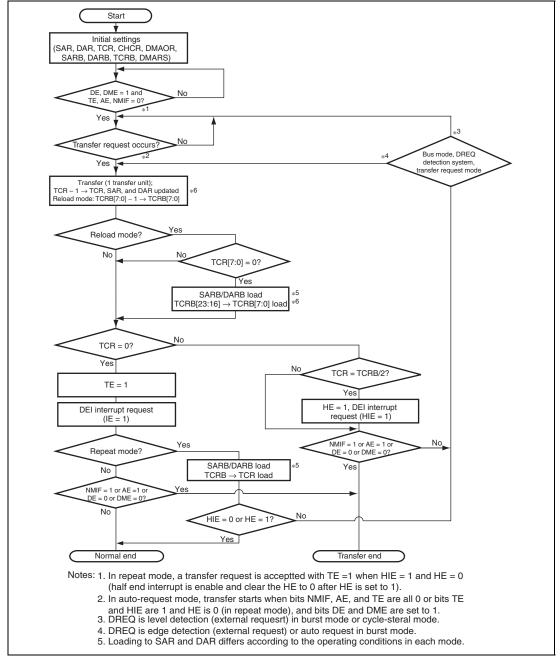

|          | 12.4.3  | DMA Transfer Types                                                  | 393 |

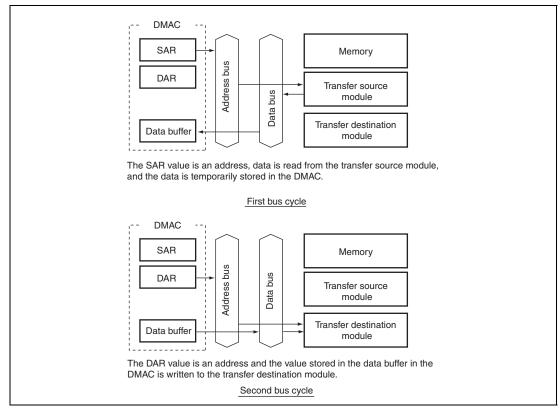

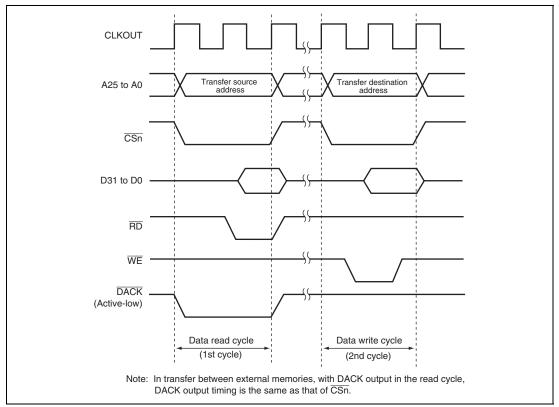

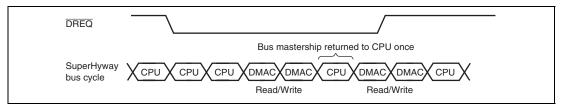

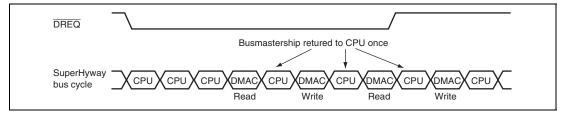

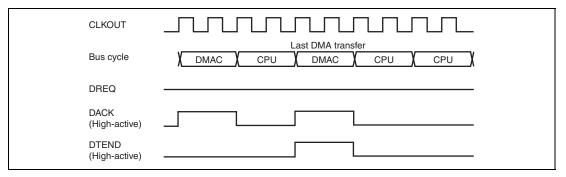

|          | 12.4.4  | DMA Transfer Flow                                                   | 400 |

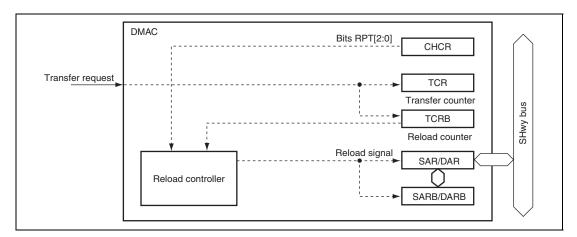

|          | 12.4.5  | Repeat Mode Transfer                                                | 402 |

|          | 12.4.6  | Reload Mode Transfer                                                | 403 |

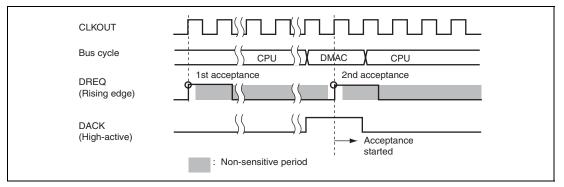

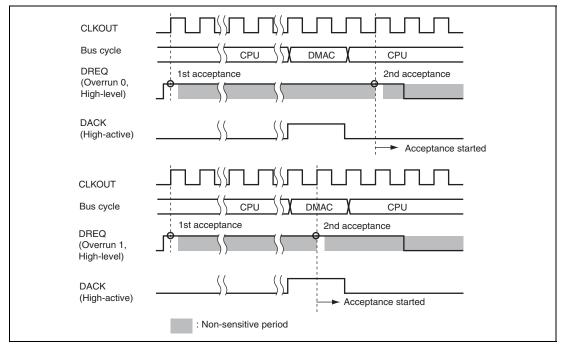

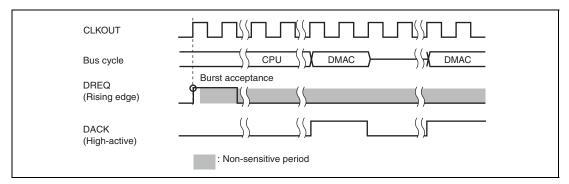

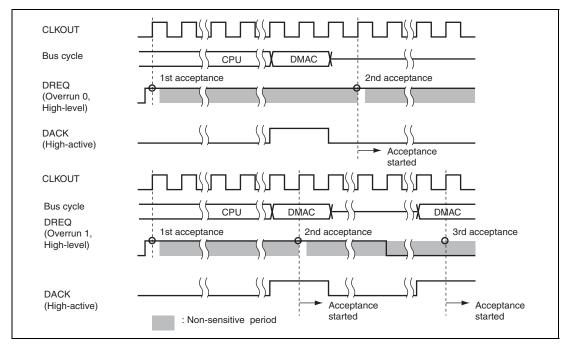

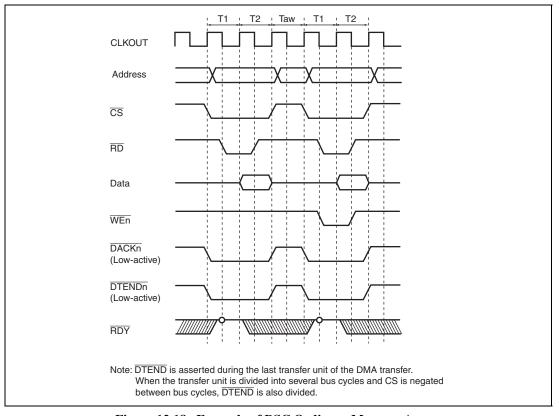

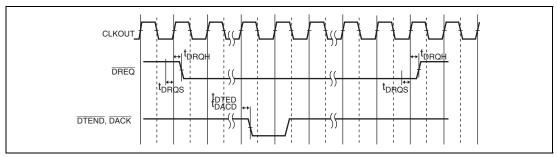

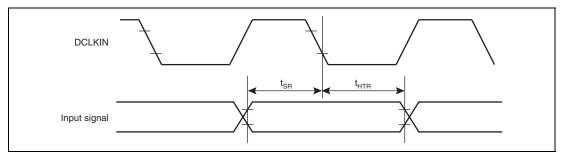

|          | 12.4.7  | DREQ Pin Sampling Timing                                            | 404 |

| 12.5     |         | Notes                                                               |     |

|          | _       | Module Stop                                                         |     |

|          |         | Address Error                                                       |     |

|          |         | Notes on Burst Mode Transfer                                        |     |

|          |         | DACK Output Division and External Request                           |     |

|          |         | DMA Transfer to DMAC Prohibited                                     |     |

|          |         | NMI Interrupt                                                       |     |

|          |         | CS Output Settings and Transfer Size Larger than External Bus Width |     |

|          |         | DACK Assertion and DREQ Sampling                                    |     |

|          |         | Duplicate Transfer Request Acceptance                               |     |

|          |         | O Clearing DMAC Flag Bit                                            |     |

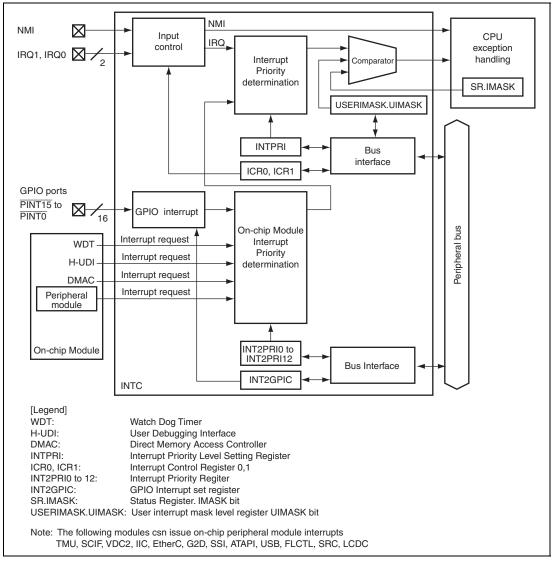

| Sect     | ion 13  | Interrupt Controller (INTC)                                         | 413 |

| 13.1     |         | 28                                                                  |     |

|          |         | Interrupt Method                                                    |     |

|          | 13.1.2  | Interrupt Types in INTC                                             | 416 |

| 13.2  | Input/C   | Output Pins                                                         | 418 |

|-------|-----------|---------------------------------------------------------------------|-----|

| 13.3  | _         | er Descriptions                                                     |     |

|       | 13.3.1    | Interrupt Control Register 0 (ICR0)                                 | 423 |

|       | 13.3.2    | Interrupt Control Register 1 (ICR1)                                 | 425 |

|       | 13.3.3    | Interrupt Priority Register (INTPRI)                                | 426 |

|       |           | Interrupt Source Register (INTREQ)                                  |     |

|       |           | Interrupt Mask Register (INTMSK)                                    |     |

|       | 13.3.6    | Interrupt Mask Clear Register (INTMSKCLR)                           | 429 |

|       |           | NMI Flag Control Register (NMIFCR)                                  |     |

|       | 13.3.8    | User Interrupt Mask Level Register (USERIMASK)                      | 432 |

|       | 13.3.9    | On-Chip Module Interrupt Priority Registers (INT2PRI0 to INT2PRI12) | 434 |

|       | 13.3.10   | Interrupt Source Register 0 (Mask State is not affected) (INT2A0)   | 436 |

|       | 13.3.11   | Interrupt Source Register 01 (Mask State is not affected) (INT2A01) | 438 |

|       | 13.3.12   | 2 Interrupt Source Register (Mask State is affected) (INT2A1)       | 440 |

|       | 13.3.13   | 3 Interrupt Source Register 11 (Mask State is affected) (INT2A11)   | 442 |

|       | 13.3.14   | Interrupt Mask Register (INT2MSKR)                                  | 444 |

|       | 13.3.15   | 5 Interrupt Mask Register 1 (INT2MSKR1)                             | 446 |

|       |           | 5 Interrupt Mask Clear Register (INT2MSKCR)                         |     |

|       | 13.3.17   | 7 Interrupt Mask Clear Register 1 (INT2MSKCR1)                      | 450 |

|       | 13.3.18   | 3 On-Chip Module Interrupt Source Registers                         |     |

|       |           | (INT2B0 and INT2B2 to INT2B7)                                       | 452 |

|       | 13.3.19   | GPIO Interrupt Set Register (INT2GPIC)                              | 457 |

| 13.4  | Interru   | pt Sources                                                          | 459 |

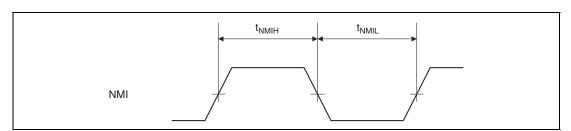

|       | 13.4.1    | NMI Interrupt                                                       | 459 |

|       |           | IRQ Interrupts                                                      |     |

|       | 13.4.3    | On-Chip Module Interrupts                                           | 460 |

|       | 13.4.4    | Interrupt Priority Level of On-Chip Module Interrupts               | 460 |

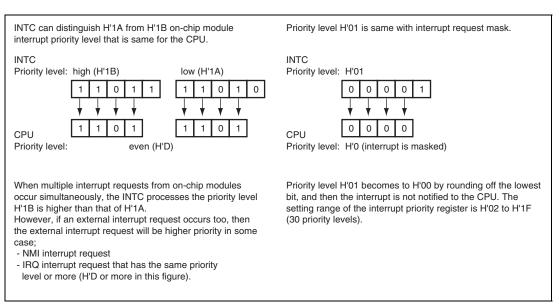

|       | 13.4.5    | Interrupt Exception Handling and Priority                           | 461 |

| 13.5  | Operation |                                                                     |     |

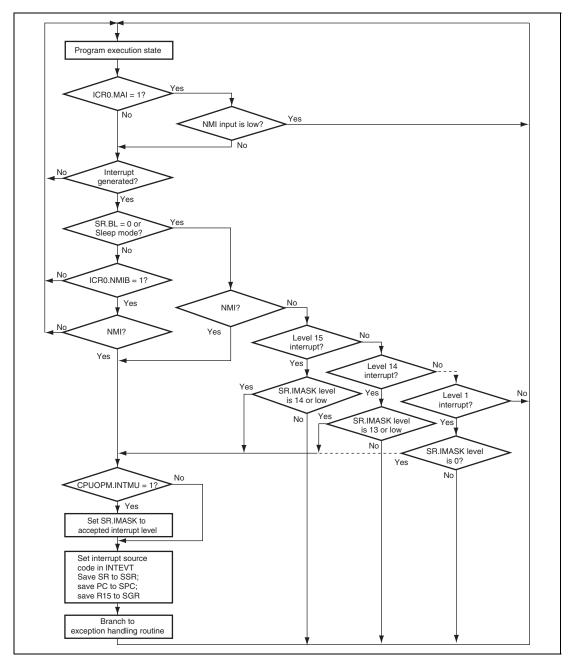

|       | 13.5.1    | Interrupt Sequence                                                  | 466 |

|       |           | Multiple Interrupts                                                 |     |

|       | 13.5.3    | Interrupt Masking by MAI Bit                                        | 468 |

| 13.6  | Interru   | pt Response Time                                                    | 469 |

| 13.7  | Usage     | Notes                                                               | 470 |

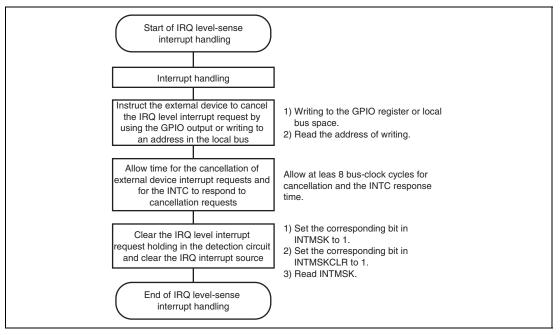

|       |           | To Clear Interrupt Request When Holding Function Selected           |     |

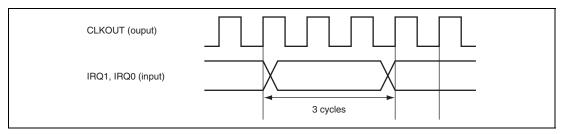

|       | 13.7.2    | Notes on Setting IRQ1 and IRQ0 Pin Function                         | 471 |

|       | 13.7.3    | To Clear IRQ Interrupt Requests                                     | 471 |

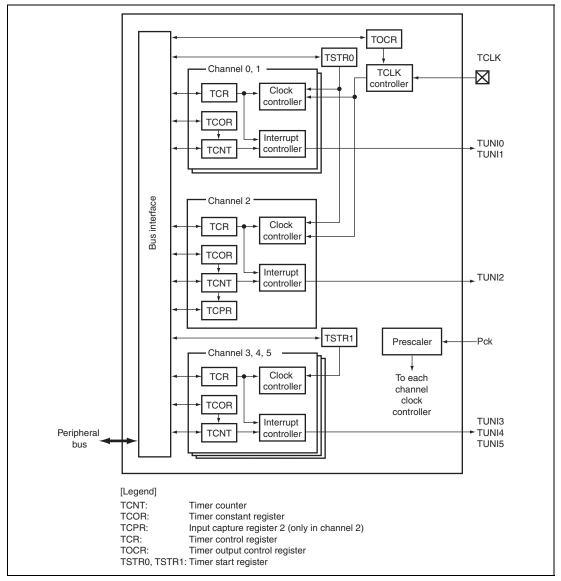

| Secti | ion 14    | Timer Unit (TMU)                                                    | 473 |

|       |           | 28.                                                                 |     |

|       |           |                                                                     |     |

| 14.2 | Input/0     | Output Pins                                     | 475 |

|------|-------------|-------------------------------------------------|-----|

| 14.3 | Registe     | er Descriptions                                 | 476 |

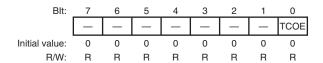

|      | 14.3.1      | Timer Output Control Register (TOCR)            | 478 |

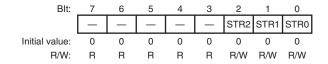

|      | 14.3.2      | Timer Start Register (TSTR0, TSTR1)             | 479 |

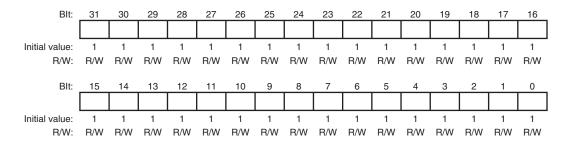

|      | 14.3.3      | Timer Constant Register (TCORn) (n = 0 to 5)    | 481 |

|      | 14.3.4      | Timer Counter (TCNTn) (n = 0 to 5)              | 481 |

|      | 14.3.5      | Timer Control Registers (TCRn) (n = 0 to 5)     | 482 |

|      | 14.3.6      | Input Capture Register 2 (TCPR2)                | 484 |

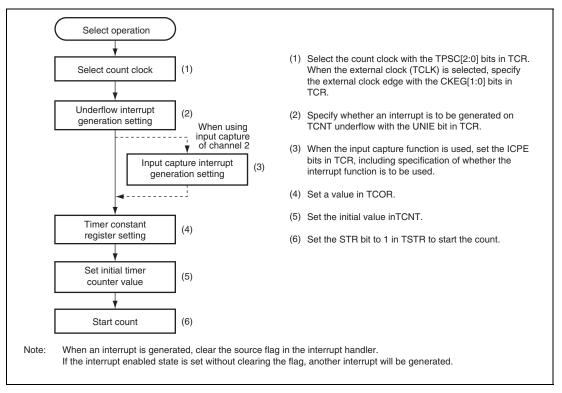

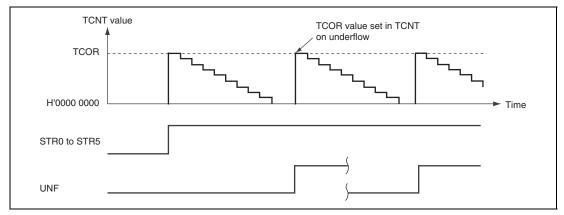

| 14.4 | Operat      | ion                                             | 485 |

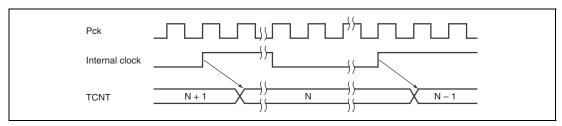

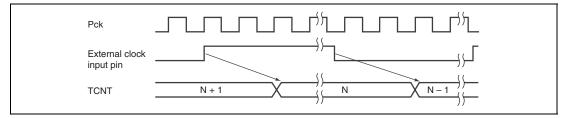

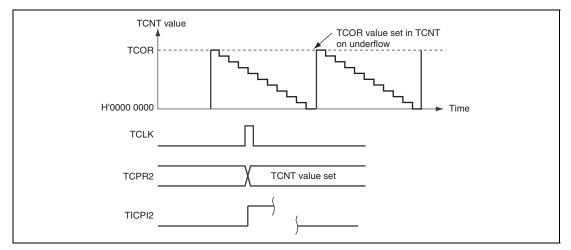

|      | 14.4.1      | Counter Operation                               | 485 |

|      | 14.4.2      | Input Capture Function                          | 488 |

| 14.5 | Interru     | pts                                             | 490 |

| 14.6 | Usage       | Notes                                           | 491 |

|      | 14.6.1      | Register Writes                                 | 491 |

|      | 14.6.2      | Reading from TCNT                               | 491 |

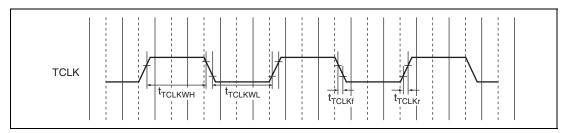

|      | 14.6.3      | External Clock Frequency                        | 491 |

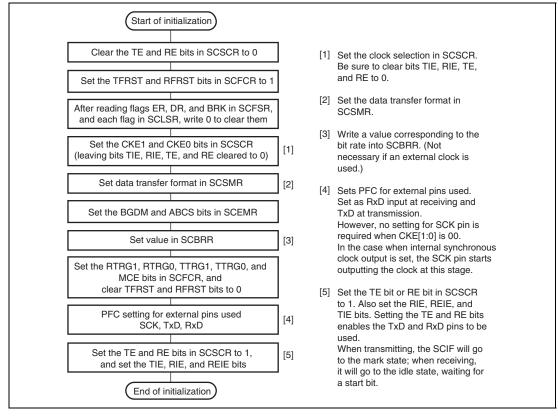

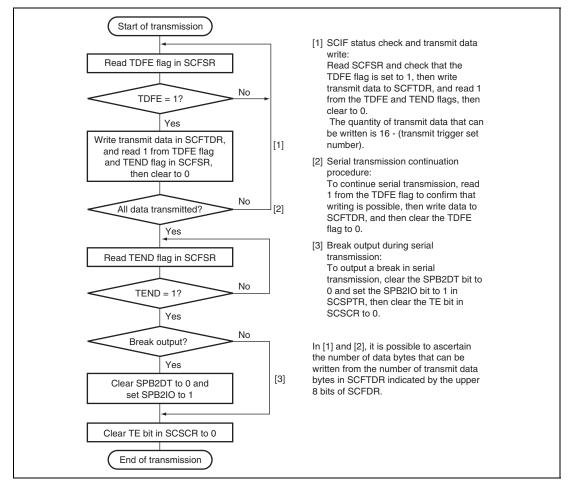

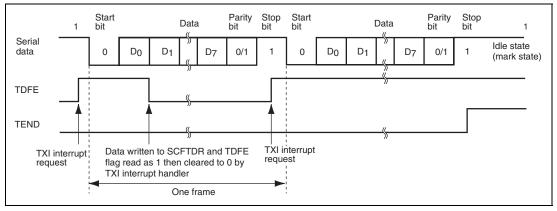

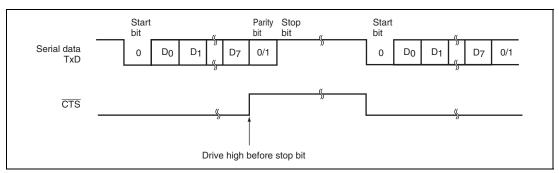

| Sect | ion 15      | Serial Communication Interface with FIFO (SCIF) | 493 |

| 15.1 |             | es                                              |     |

| 15.2 | Input/0     | Output Pins                                     | 496 |

| 15.3 | Registe     | er Descriptions                                 | 497 |

|      | 15.3.1      | Receive Shift Register (SCRSR)                  | 500 |

|      | 15.3.2      | Receive FIFO Data Register (SCFRDR)             | 500 |

|      | 15.3.3      | Transmit Shift Register (SCTSR)                 | 501 |

|      |             | Transmit FIFO Data Register (SCFTDR)            |     |

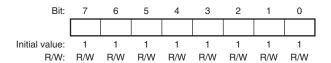

|      | 15.3.5      | Serial Mode Register (SCSMR)                    | 502 |

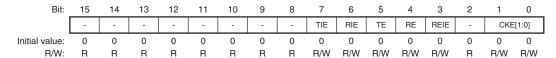

|      | 15.3.6      | Serial Control Register (SCSCR)                 | 505 |

|      | 15.3.7      | Serial Status Register (SCFSR)                  | 509 |

|      | 15.3.8      | Bit Rate Register (SCBRR)                       | 517 |

|      | 15.3.9      | FIFO Control Register (SCFCR)                   | 522 |

|      | 15.3.10     | ) FIFO Data Count Set Register (SCFDR)          | 525 |

|      | 15.3.1      | 1 Serial Port Register (SCSPTR)                 | 526 |

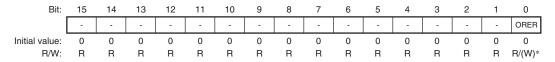

|      | 15.3.12     | 2 Line Status Register (SCLSR)                  | 529 |

|      |             | 3 Serial Extension Mode Register (SCEMR)        |     |

| 15.4 |             | ion                                             |     |

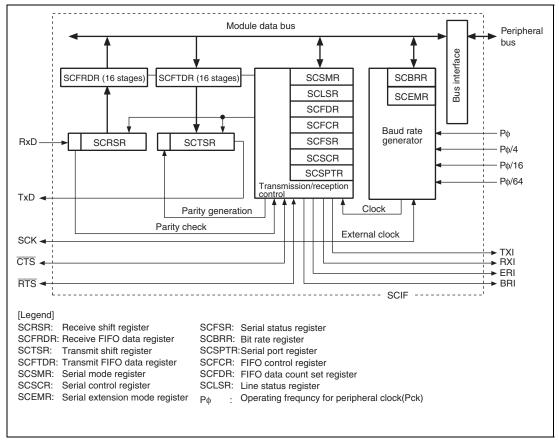

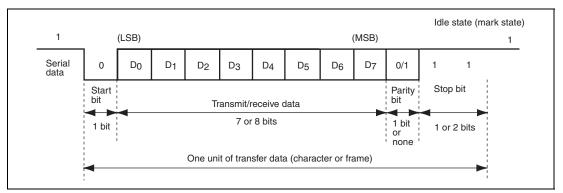

|      | 15.4.1      | Overview                                        | 531 |

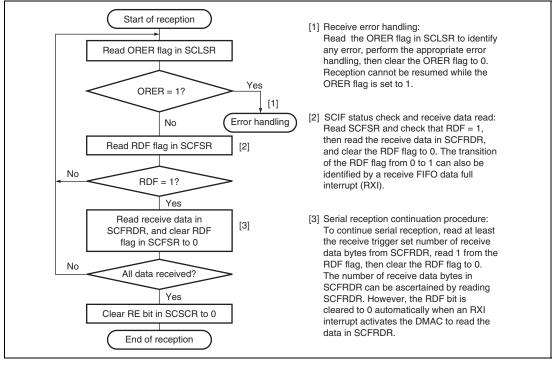

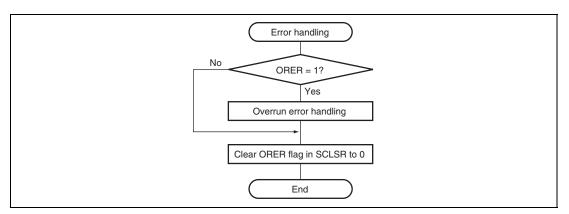

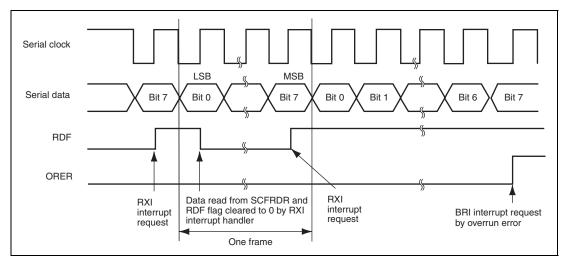

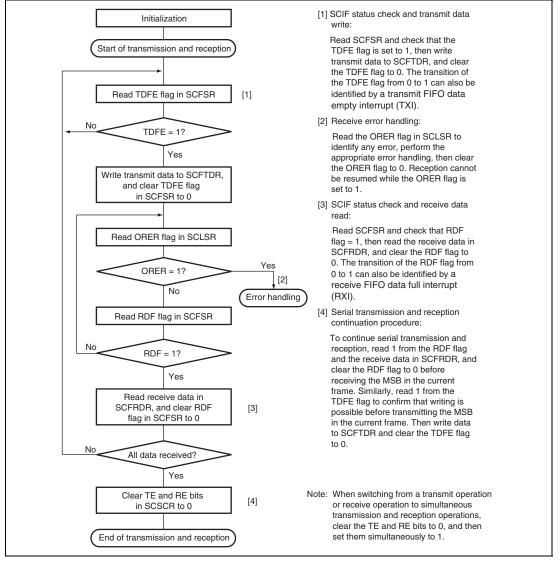

|      | 15.4.2      | Operation in Asynchronous Mode                  | 534 |

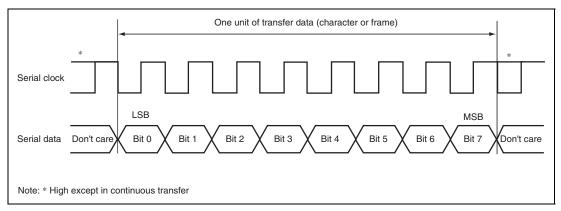

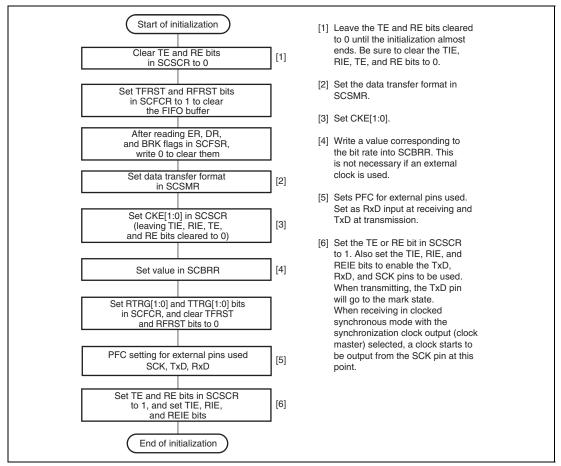

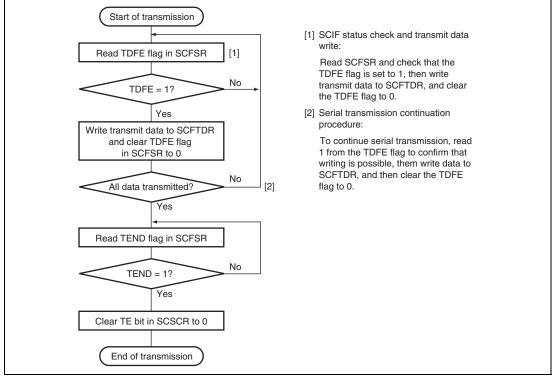

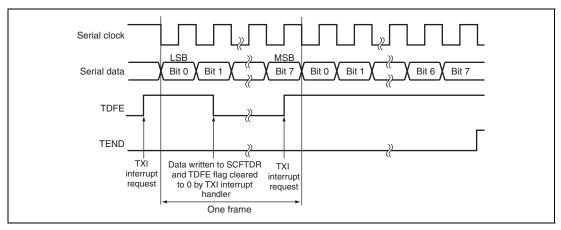

|      |             | Operation in Clock Synchronous Mode             |     |

| 15.5 |             | nterrupts                                       |     |

| 15.6 | Usage Notes |                                                 |     |

|               | 15.6.1 | SCFTDR Writing and TDFE Flag                                        | 554 |

|---------------|--------|---------------------------------------------------------------------|-----|

|               |        | SCFRDR Reading and RDF Flag                                         |     |

|               |        | Break Detection and Processing                                      |     |

|               |        | Sending a Break Signal                                              |     |

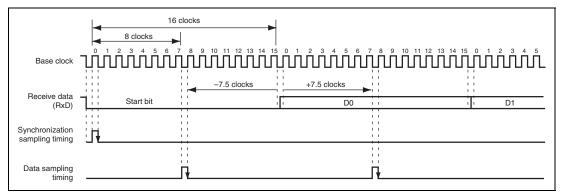

|               |        | Receive Data Sampling Timing and Receive Margin (Asynchronous Mode) |     |

|               |        | Selection of Base Clock in Asynchronous Mode                        |     |

| Soot          | ion 16 | I <sup>2</sup> C Bus Interface (IIC)                                | 550 |

| 300i.<br>16.1 |        | es                                                                  |     |

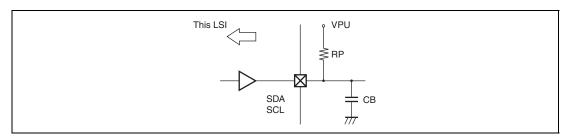

| 16.2          |        | Output Pins                                                         |     |

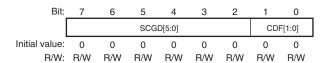

| 16.3          | -      | er Descriptions                                                     |     |

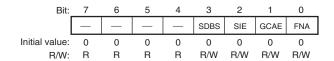

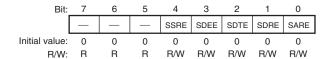

| 10.5          | _      | Slave Control Register (ICSCR)                                      |     |

|               |        | Slave Status Register (ICSSR)                                       |     |

|               |        | Slave Interrupt Enable Register (ICSIER)                            |     |

|               |        | Slave Address Register (ICSAR)                                      |     |

|               |        | Master Control Register (ICMCR)                                     |     |

|               |        | Master Status Register (ICMSR)                                      |     |

|               |        | Master Interrupt Enable Register (ICMIER)                           |     |

|               |        | · · · · · · · · · · · · · · · · · · ·                               |     |

|               |        | Master Address Register (ICMAR)                                     |     |

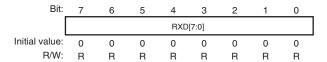

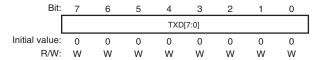

|               |        | Receive and Transmit Data Registers (ICRXD and ICTXD)               |     |

| 16.4          |        |                                                                     |     |

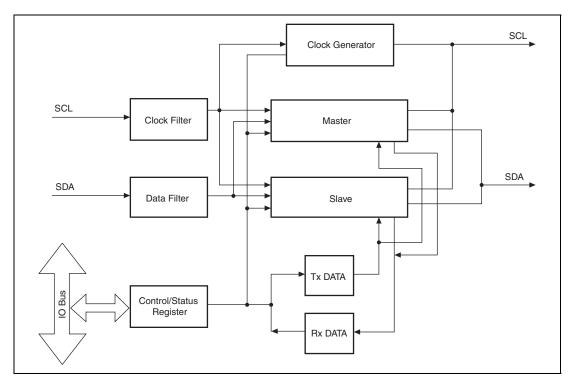

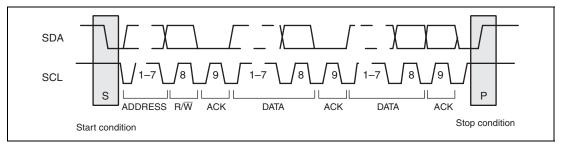

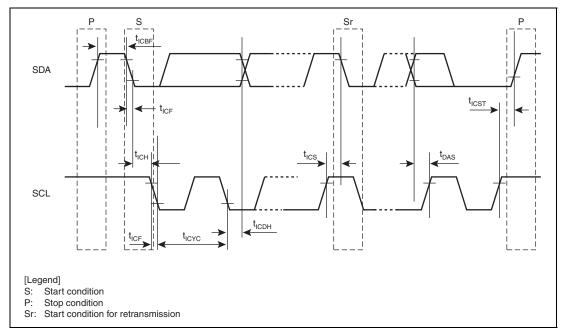

| 16.4          |        | ons                                                                 |     |

|               |        |                                                                     |     |

|               |        | Clock Generator                                                     |     |

|               |        | Master/Slave Interfaces.                                            |     |

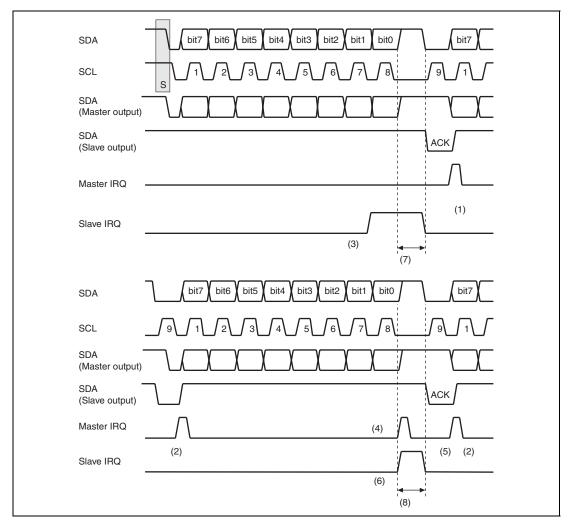

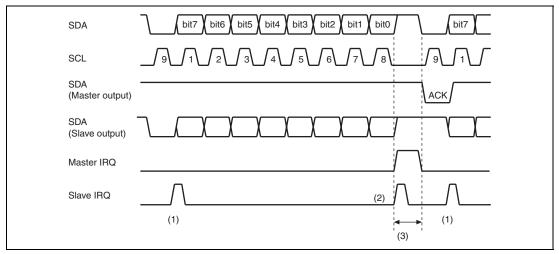

|               |        | Software Status Interlocking                                        |     |

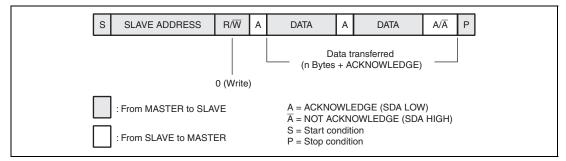

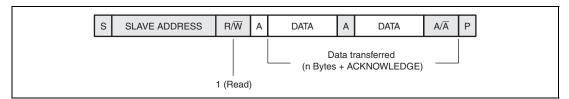

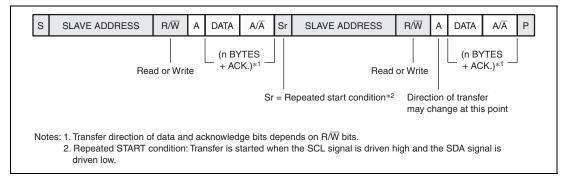

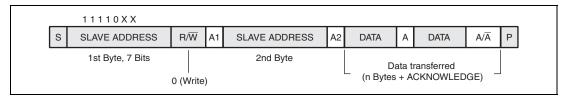

|               |        | I <sup>2</sup> C Bus Data Format                                    |     |

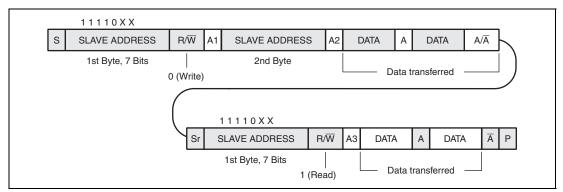

|               |        | 7-Bit Address Format.                                               |     |

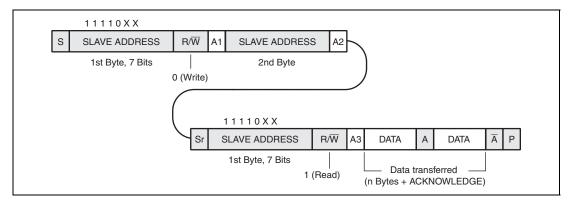

|               |        | 10-Bit Address Format.                                              |     |

|               |        | Master Transmit Operation                                           |     |

| 165           |        | Master Receive Operation                                            |     |

| 16.5          |        | Operation                                                           |     |

|               |        | Slave Address Receive Operation.                                    |     |

|               |        | Slave Data Receive Operation                                        |     |

| 166           |        | Slave Data Transmit Operation                                       |     |

| 16.6          | _      | mming Examples                                                      |     |

|               |        | Master Transmitter                                                  |     |

|               |        | Master Receiver                                                     |     |

|               | 16.6.3 | Master Transmitter - Restart - Master Receiver                      | 589 |

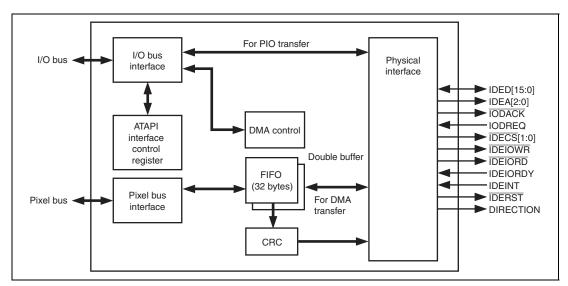

| Sect | ion 17                           | ATAPI                                                  | 591 |

|------|----------------------------------|--------------------------------------------------------|-----|

| 17.1 | Feature                          | es                                                     | 591 |

| 17.2 | Input/C                          | Output Pins                                            | 592 |

| 17.3 | Registe                          | er Description                                         | 593 |

|      | 17.3.1                           | ATAPI Control (ATAPI_CONTROL)                          | 596 |

|      | 17.3.2                           | ATAPI Status (ATAPI_STATUS)                            | 598 |

|      | 17.3.3                           | Interrupt Enable (ATAPI_INT_ENABLE)                    | 600 |

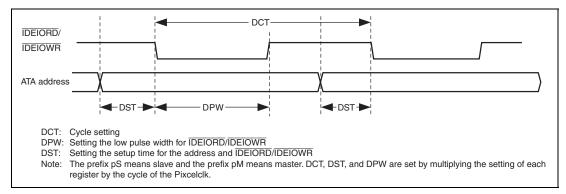

|      |                                  | PIO Timing Register (ATAPI_PIO_TIMING)                 |     |

|      | 17.3.5                           | Multiword DMA Timing Register (ATAPI_MULTI_TIMING)     | 602 |

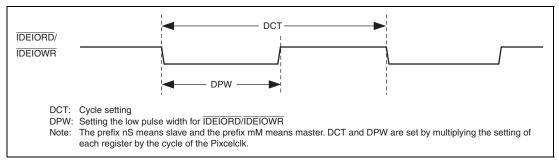

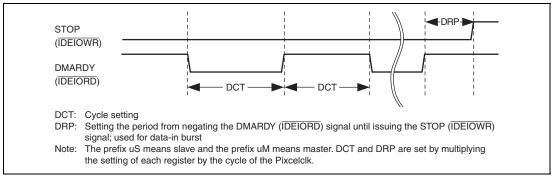

|      | 17.3.6                           | Ultra DMA Timing Register (ATAPI_ULTRA_TIMING)         | 604 |

|      | 17.3.7                           | Descriptor Table Base Address Register (ATAPI_DTB_ADR) | 605 |

|      | 17.3.8                           | Descriptor Table                                       | 606 |

|      | 17.3.9                           | Termination Flag and Descriptor DMA Start Address      | 607 |

|      | 17.3.10                          | Descriptor DMA Transfer Count                          | 608 |

|      | 17.3.11                          | DMA Start Address Register (ATAPI_DMA_START_ADR)       | 609 |

|      | 17.3.12                          | 2 DMA Transfer Count Register (ATAPI_DMA_TRANS_CNT)    | 610 |

|      | 17.3.13                          | 3 ATAPI Control 2 (ATAPI_CONTROL2)                     | 611 |

|      | 17.3.14                          | 4 ATAPI Signal Status Register (ATAPI_SIG_ST)          | 612 |

|      | 17.3.15                          | 5 Byteswap (ATAPI_BYTE_SWAP)                           | 613 |

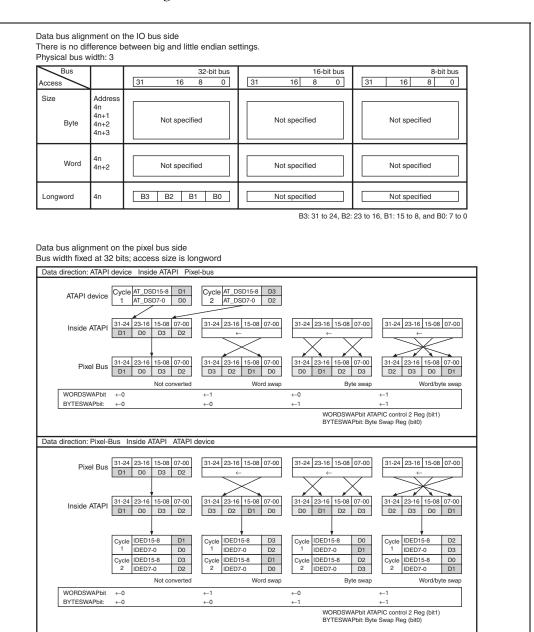

|      | 17.3.16 ATAPI Data Bus Alignment |                                                        | 614 |

| 17.4 | Functional Description           |                                                        |     |

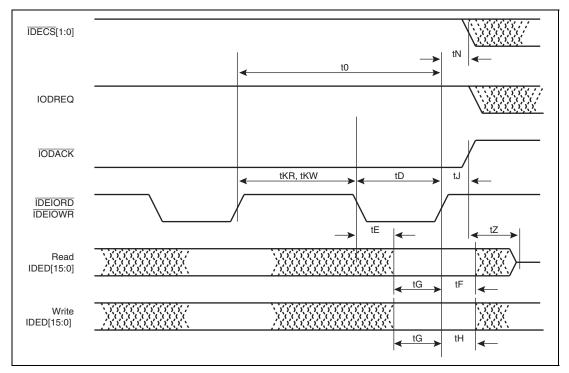

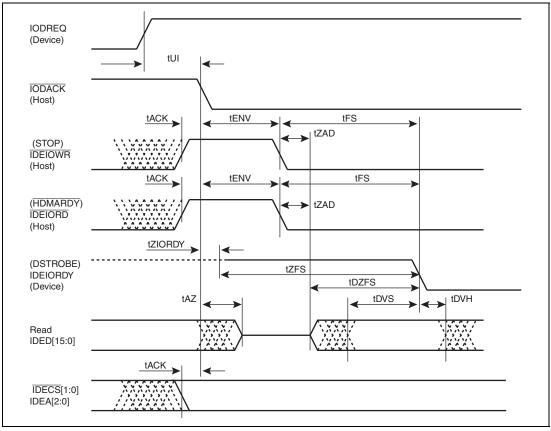

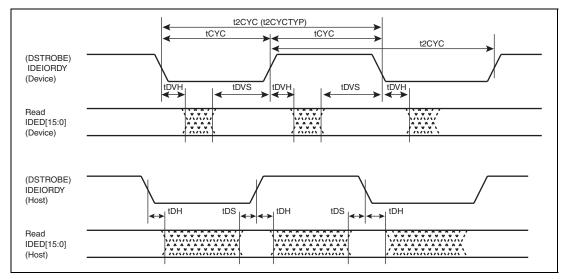

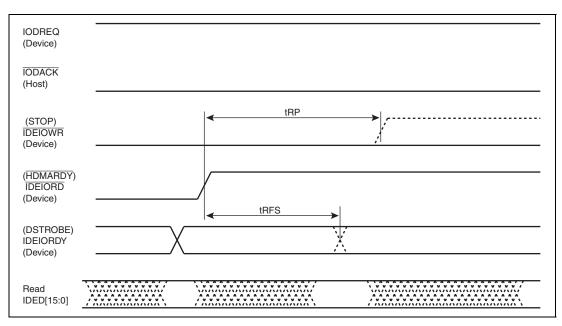

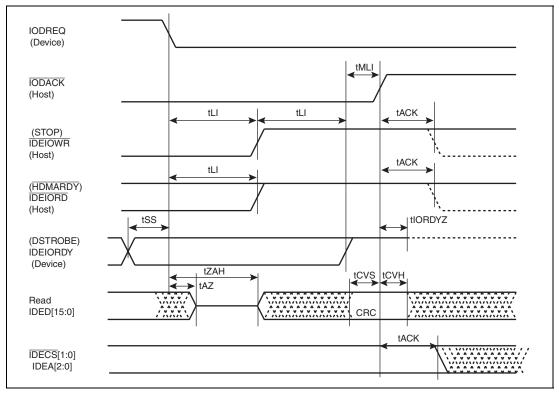

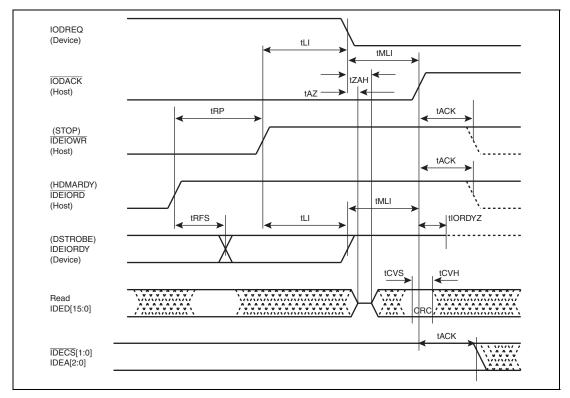

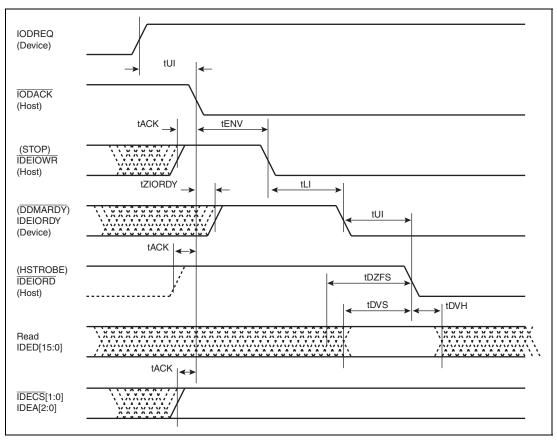

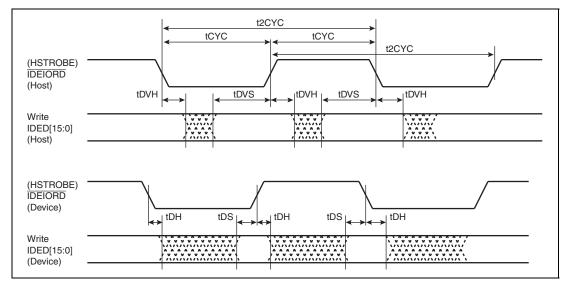

|      | 17.4.1                           | Data Transfer Modes                                    | 615 |

|      | 17.4.2                           | Descriptor Function                                    | 615 |

| 17.5 | Operating Procedure              |                                                        |     |

|      | 17.5.1                           | Initialization                                         | 616 |

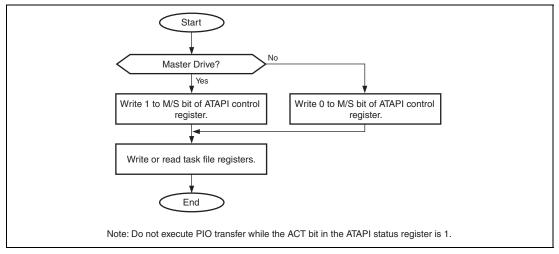

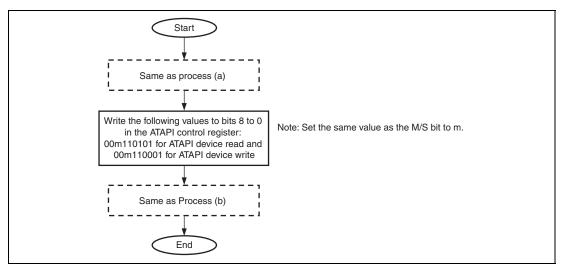

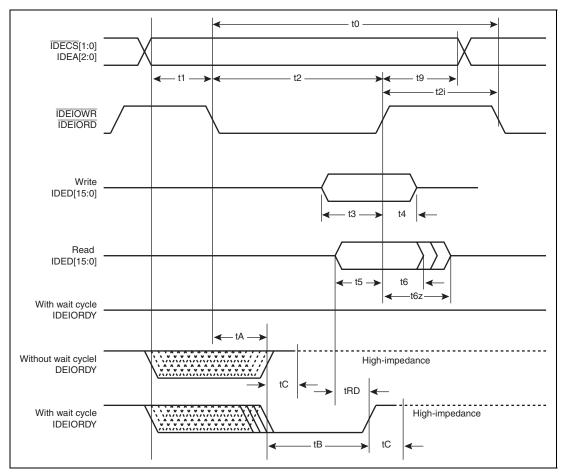

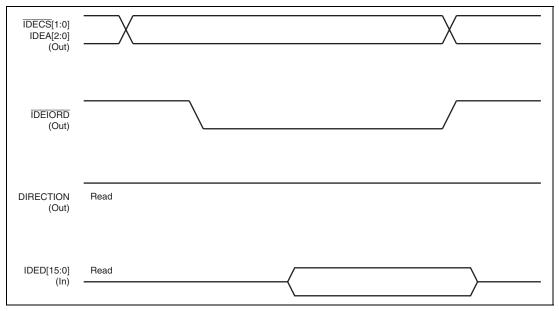

|      | 17.5.2                           | Procedure in PIO Transfer Mode                         | 616 |

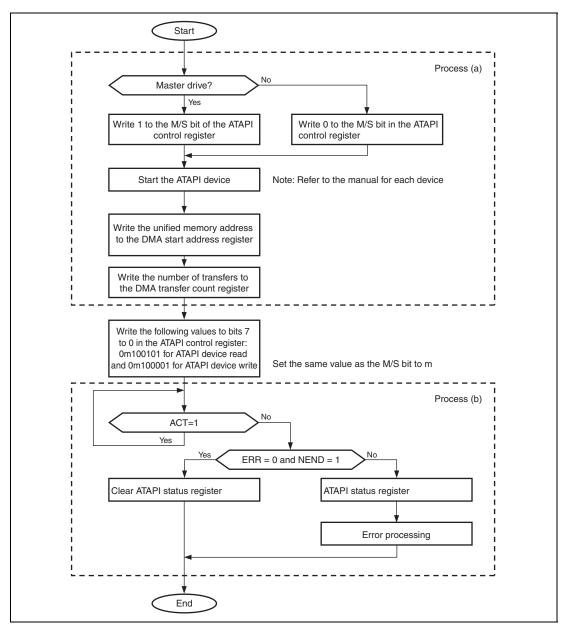

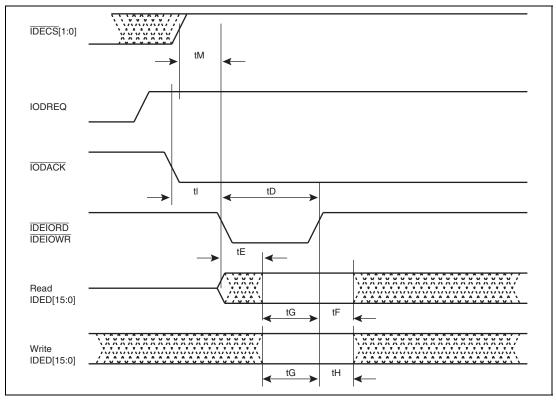

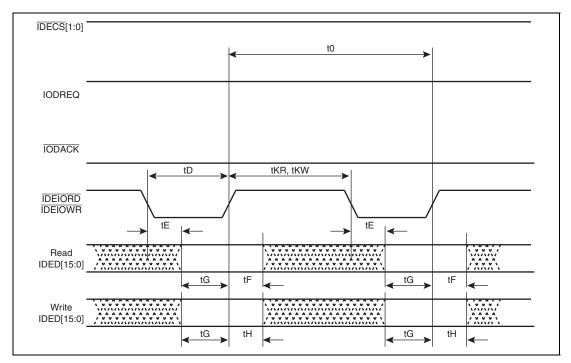

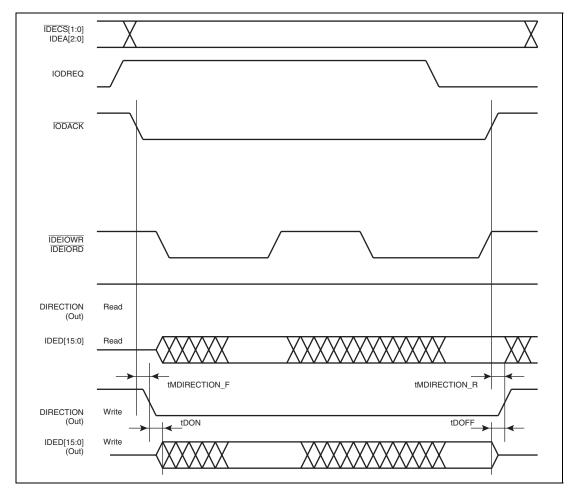

|      | 17.5.3                           | Procedure in Multiword DMA Transfer Mode               | 617 |

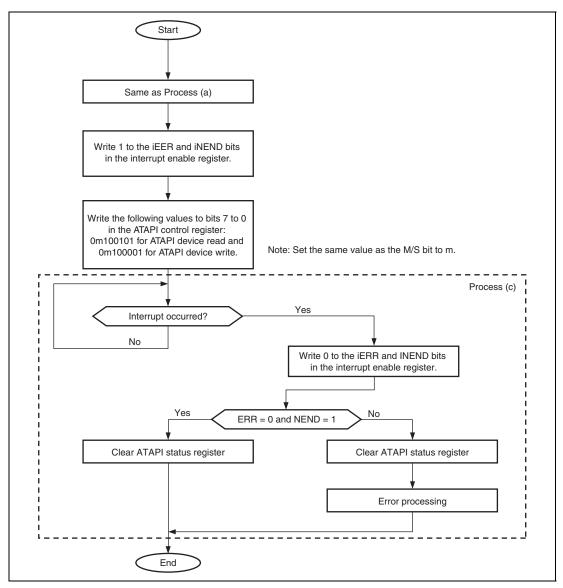

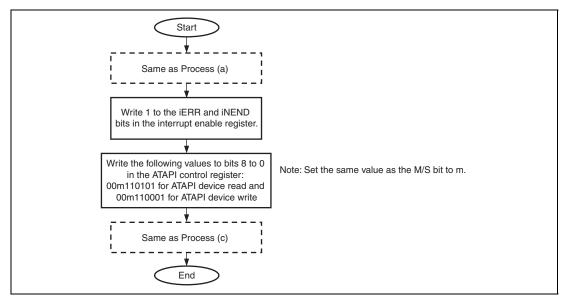

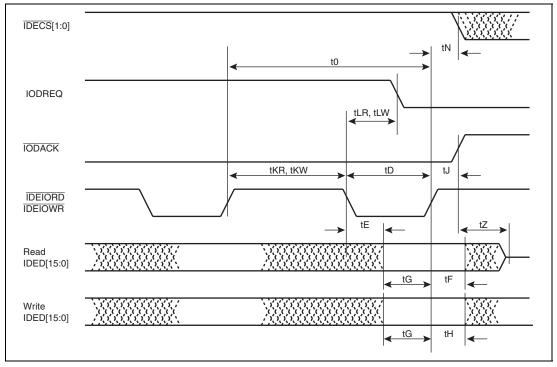

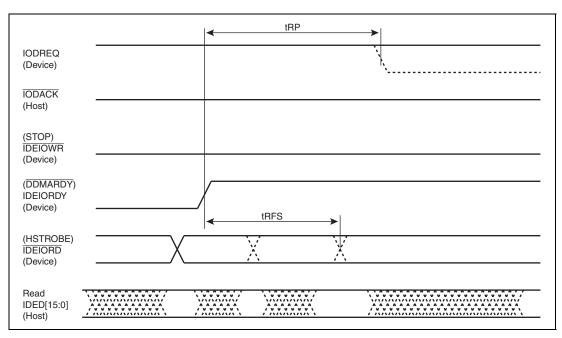

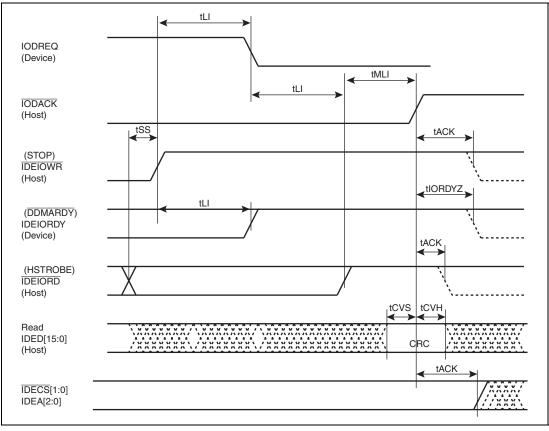

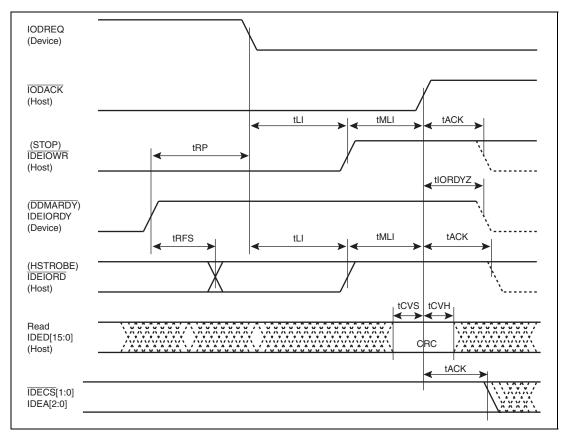

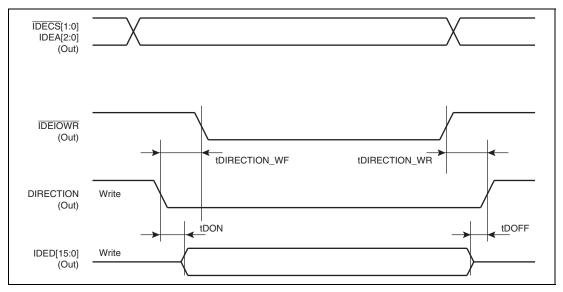

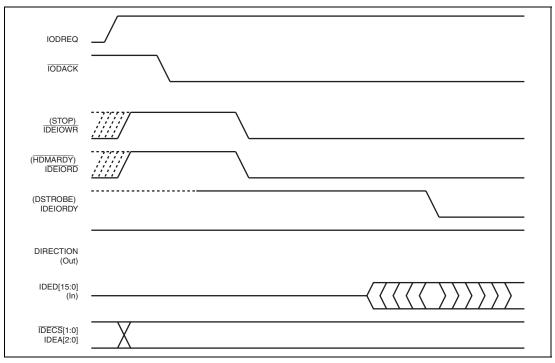

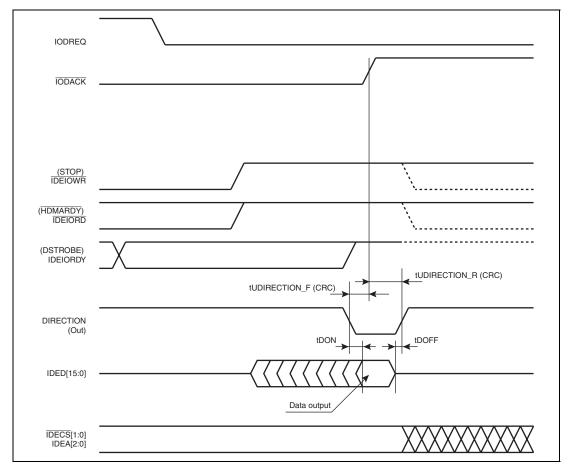

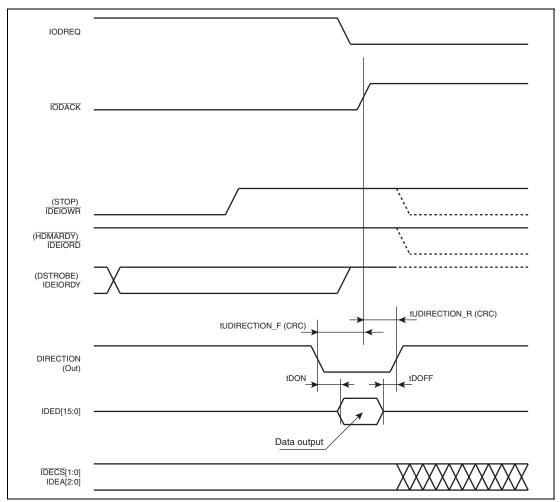

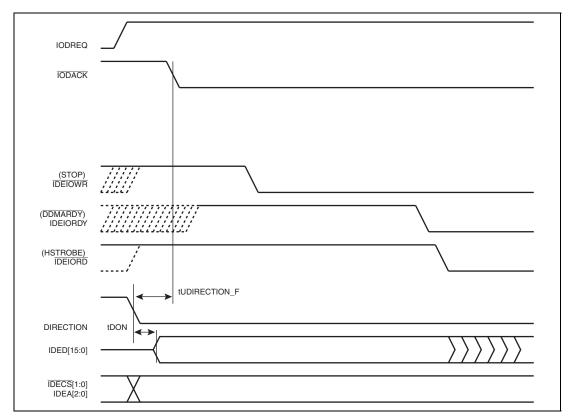

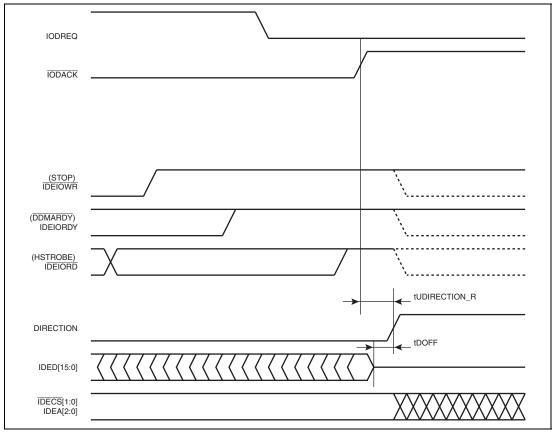

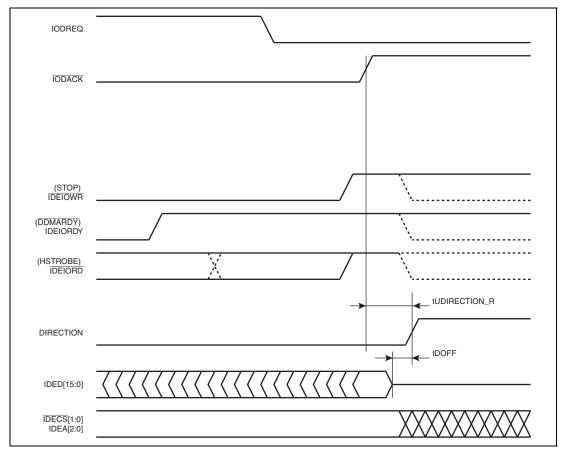

|      | 17.5.4                           | Procedure in Ultra DMA Transfer Mode                   | 620 |

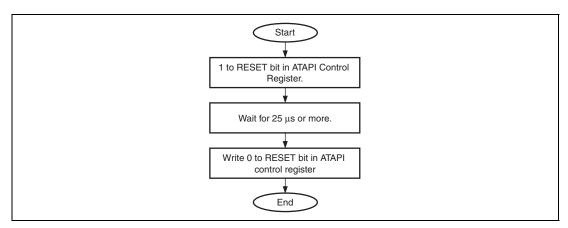

|      | 17.5.5                           | Procedure in Hardware Reset for ATAPI Device           | 621 |

| 17.6 | Usage                            | Note                                                   | 622 |

|      | 17.6.1                           | Erroneous Detection of IORDY Timeout                   | 622 |

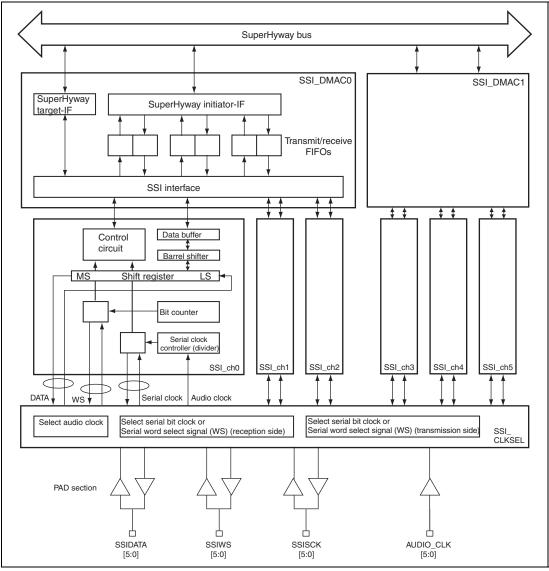

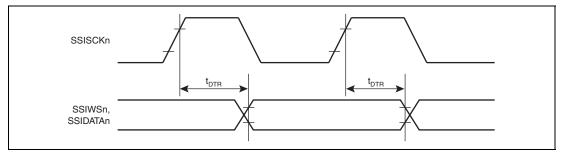

| Sect | ion 18                           | Serial Sound Interface (SSI)                           | 623 |

| 18.1 | Feature                          | es                                                     | 623 |

|      | 18.1.1                           | SSI Module Configuration                               | 623 |

|      | 18.1.2                           | SSI Features                                           | 623 |

| 18.2 |                                  | Output Pins                                            |     |

| 18.3 | Registe                          | er Descriptions                                        | 625 |

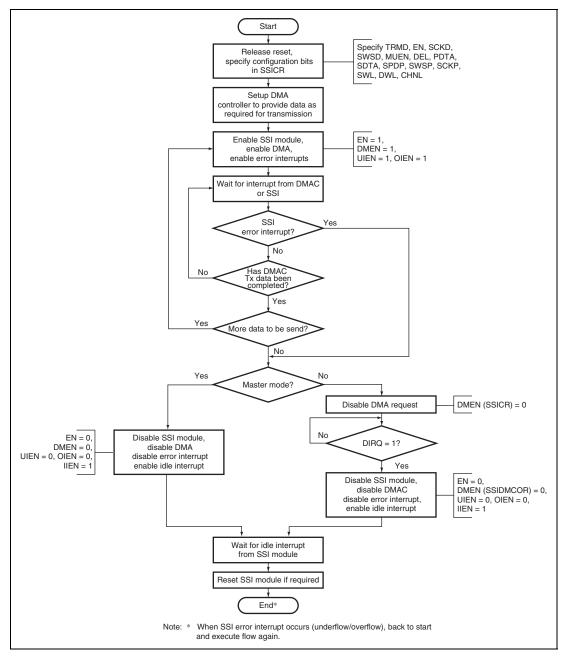

|      | 18.3.1                           | DMA Mode Registers 0 to 5 (SSIDMMR0 to SSIDMMR5)       | 637 |

|      | 18.3.2        | RDMA Transfer Source Address Registers 0 to 5                     |     |

|------|---------------|-------------------------------------------------------------------|-----|

|      |               | (SSIRDMADR0 to SSIRDMADR5)                                        | 639 |

|      | 18.3.3        | RDMA Transfer Word Count Registers 0 to 5                         |     |

|      |               | (SSIRDMCNTR0 to SSIRDMCNTR5)                                      | 640 |

|      | 18.3.4        | WDMA Transfer Destination Address Registers 0 to 5                |     |

|      |               | (SSIWDMADR0 to SSIWDMADR5)                                        | 641 |

|      | 18.3.5        | WDMA Transfer Word Count Registers 0 to 5                         |     |

|      |               | (SSIWDMCNTR0 to SSIWDMCNTR5)                                      | 642 |

|      | 18.3.6        | DMA Control Registers 0 to 5 (SSIDMCOR0 to SSIDMCOR5)             | 643 |

|      | 18.3.7        | Transmit Suspension Block Counters 0 to 5                         |     |

|      |               | (SSISTPBLCNT0 to SSISTPBLCNT5)                                    | 654 |

|      | 18.3.8        | Transmit Suspension Transfer Data Registers 0 to 5                |     |

|      |               | (SSISTPDR0 to SSISTPDR5)                                          |     |

|      |               | Block Count Source Registers 0 to 5 (SSIBLCNTSR0 to SSIBLCNTSR5)  |     |

|      |               | Block Counters 0 to 5 (SSIBLCNT0 to SSIBLCNT5)                    | 657 |

|      | 18.3.11       | n-Times Block Transfer Interrupt Count Source Registers 0 to 5    |     |

|      |               | (SSIBLNCNTSR0 to SSIBLNCNTSR5)                                    | 658 |

|      | 18.3.12       | n-Times Block Counters 0 to 5 (SSIBLNCNT0 to SSIBLNCNT5)          | 659 |

|      | 18.3.13       | DMA Operation Registers 0 and 1 (SSIDMAOR0 and SSIDMAOR1)         | 660 |

|      |               | Interrupt Status Registers 0 and 1 (SSIDMINTSR0 and SSIDMINTSR1)  |     |

|      | 18.3.15       | Interrupt Mask Registers 0 and 1 (SSIDMINTMR0 and SSIDMINTMR1)    | 667 |

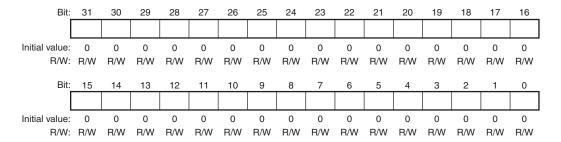

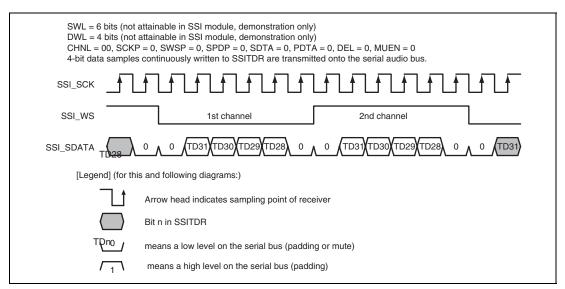

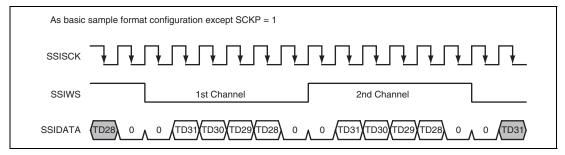

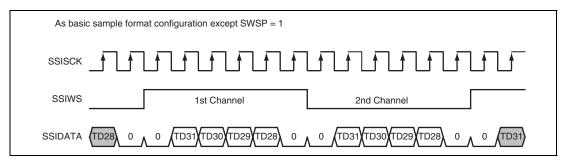

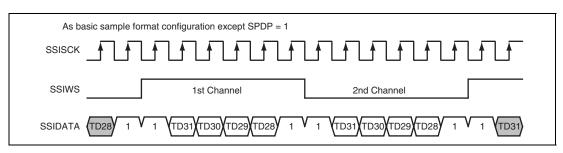

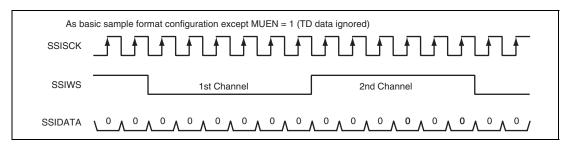

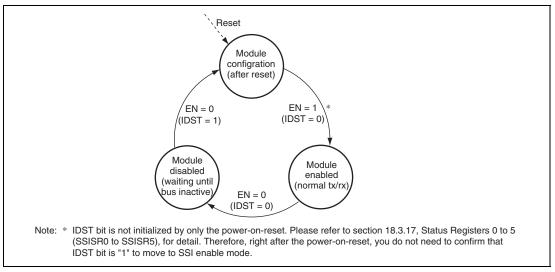

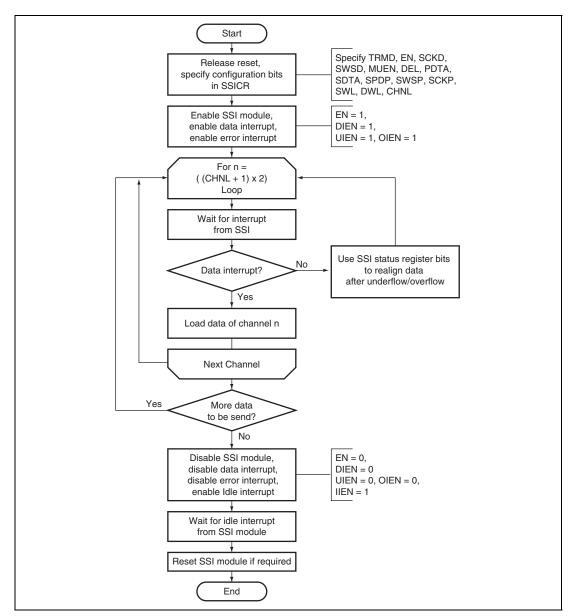

|      | 18.3.16       | Control Registers 0 to 5 (SSICR0 to SSICR5)                       | 670 |

|      |               | Status Registers 0 to 5 (SSISR0 to SSISR5)                        |     |

|      |               | Transmit Data Registers 0 to 5 (SSITDR0 to SSITDR5)               |     |

|      | 18.3.19       | Receive Data Registers 0 to 5 (SSIRDR0 to SSIRDR5)                | 681 |

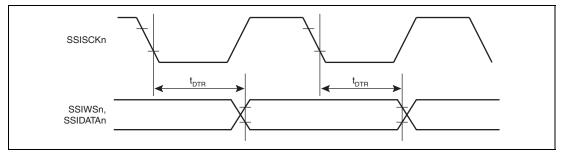

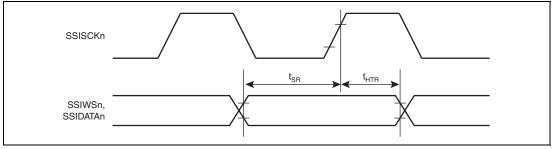

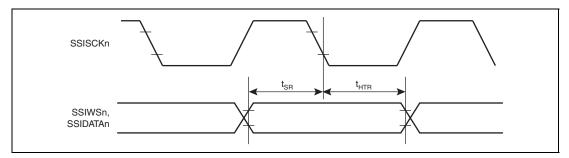

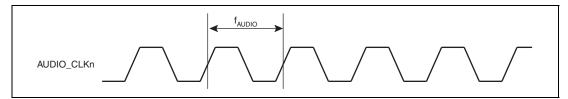

| 18.4 | -             | on                                                                |     |

|      |               | Operation of SSI_CLKSEL                                           |     |

|      |               | Operation of SSI_DMAC0 and SSI_DMAC1                              |     |

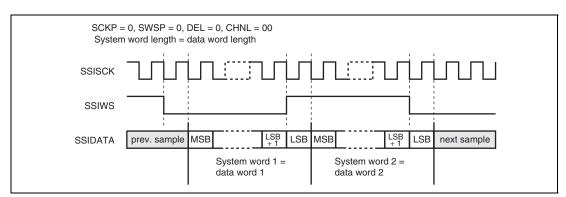

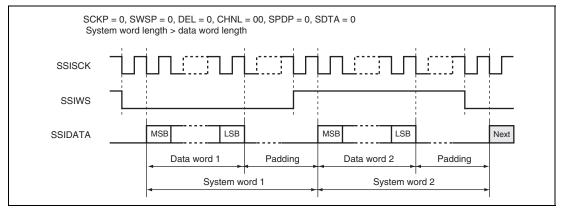

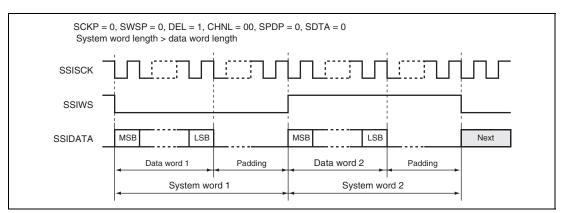

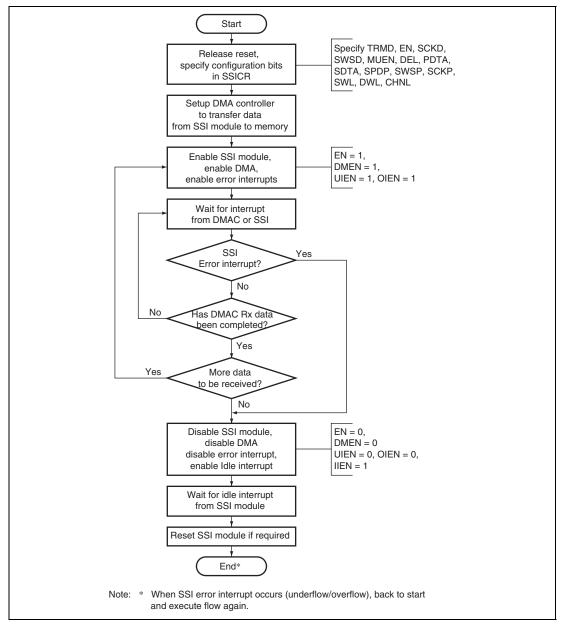

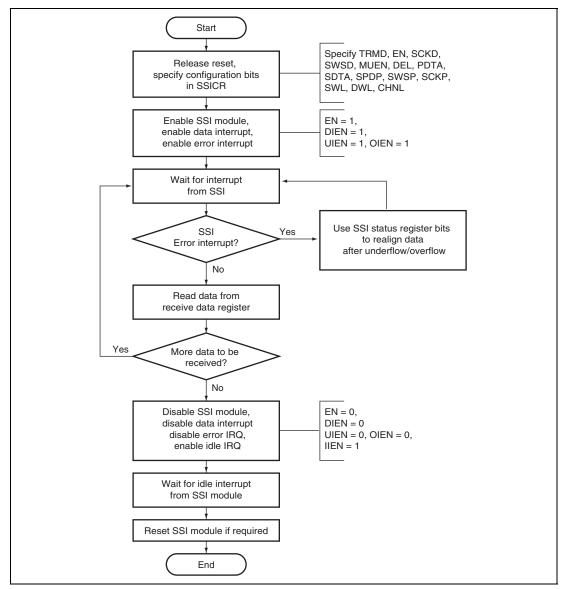

|      | 18.4.3        | Operation of SSI_CH0 to SSI_CH5                                   | 684 |

| 18.5 | $\mathcal{L}$ | Note                                                              |     |

|      |               | Restrictions when an Overflow Occurs during Receive DMA Operation |     |

|      |               | Restrictions during Operation in Slave Mode                       |     |

|      |               | Restrictions when Specify Each Register                           |     |

|      |               | Restrictions when stop Transmitting DMAC forcibly                 |     |

|      |               | Restrictions when stop Receiving DMAC forcibly                    |     |

|      |               | Restrictions when stop Transmitting/Receiving DMAC automatically  |     |

|      | 18.5.7        | Restrictions when read Block counter and n-times block counter    | 706 |

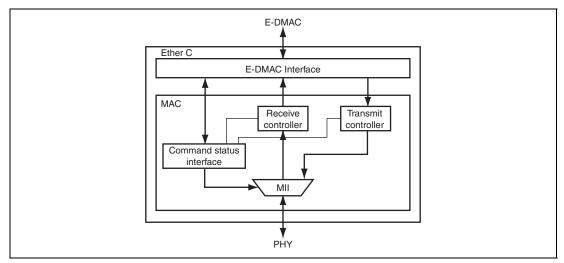

| Sect | ion 19        | Ethernet Controller (EtherC)                                      | 707 |

| 19 1 | Feature       | S.                                                                | 707 |

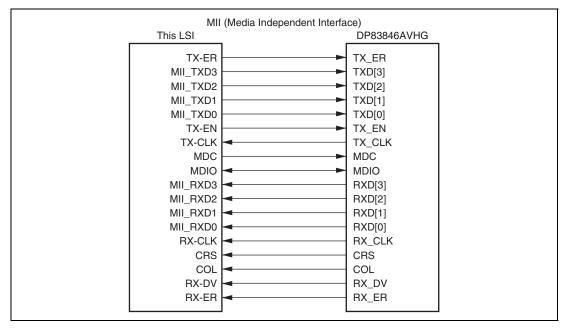

| 19.2 | Input/Output Pins                                                     | 708 |

|------|-----------------------------------------------------------------------|-----|

| 19.3 | Register Descriptions                                                 | 709 |

|      | 19.3.1 EtherC Mode Register (ECMR)                                    | 711 |

|      | 19.3.2 EtherC Status Register (ECSR)                                  | 715 |

|      | 19.3.3 EtherC Interrupt Permission Register (ECSIPR)                  | 717 |

|      | 19.3.4 PHY Interface Register (PIR)                                   | 718 |

|      | 19.3.5 MAC Address High Register (MAHR)                               | 719 |

|      | 19.3.6 MAC Address Low Register (MALR)                                | 720 |

|      | 19.3.7 Receive Frame Length Register (RFLR)                           | 721 |

|      | 19.3.8 PHY Status Register (PSR)                                      | 722 |

|      | 19.3.9 Transmit Retry Over Counter Register (TROCR)                   | 723 |

|      | 19.3.10 Delayed Collision Detect Counter Register (CDCR)              | 724 |

|      | 19.3.11 Lost Carrier Counter Register (LCCR)                          |     |

|      | 19.3.12 Carrier Not Detect Counter Register (CNDCR)                   | 726 |

|      | 19.3.13 CRC Error Frame Receive Counter Register (CEFCR)              | 727 |

|      | 19.3.14 Frame Receive Error Counter Register (FRECR)                  | 728 |

|      | 19.3.15 Too-Short Frame Receive Counter Register (TSFRCR)             | 729 |

|      | 19.3.16 Too-Long Frame Receive Counter Register (TLFRCR)              |     |

|      | 19.3.17 Residual-Bit Frame Receive Counter Register (RFCR)            | 731 |

|      | 19.3.18 Multicast Address Frame Receive Counter Register (MAFCR)      | 732 |

|      | 19.3.19 IPG Register (IPGR)                                           | 733 |

|      | 19.3.20 Automatic PAUSE Frame Register (APR)                          | 734 |

|      | 19.3.21 Manual PAUSE Frame Register (MPR)                             | 735 |

|      | 19.3.22 Automatic PAUSE Frame Retransmit Count Register (TPAUSER)     | 736 |

|      | 19.3.23 Random Number Generation Counter Upper Limit Setting Register |     |

|      | (RDMLR)                                                               | 737 |

|      | 19.3.24 PAUSE Frame Receive Counter Register (RFCF)                   | 738 |

|      | 19.3.25 PAUSE Frame Retransmit Counter Register (TPAUSECR)            | 739 |

|      | 19.3.26 Broadcast Frame Receive Count Setting Register (BCFRR)        | 740 |

| 19.4 | Operation                                                             | 741 |

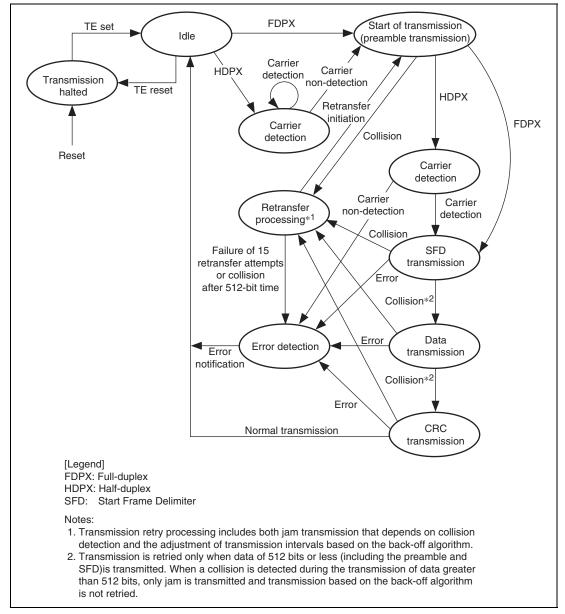

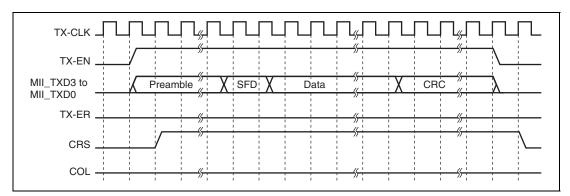

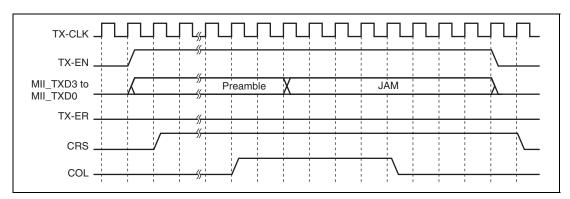

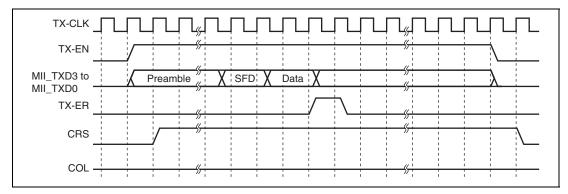

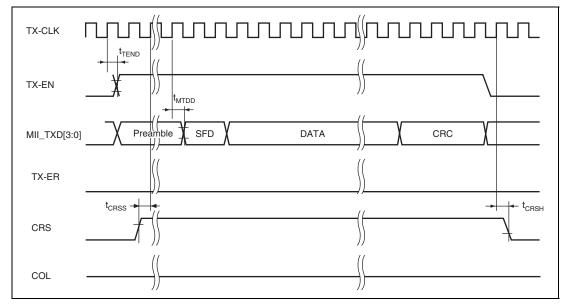

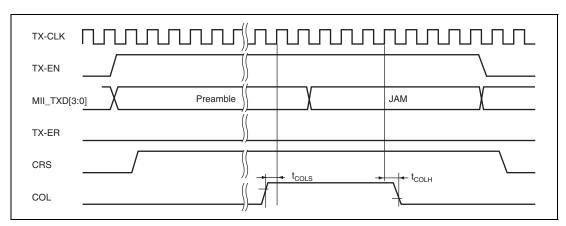

|      | 19.4.1 Transmission                                                   | 741 |

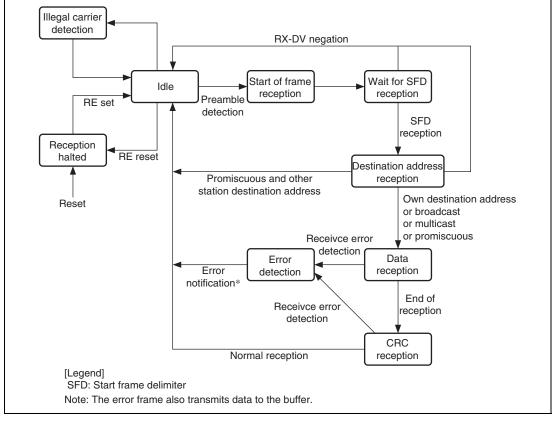

|      | 19.4.2 Reception                                                      | 743 |

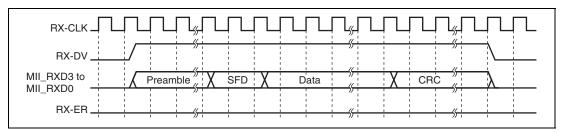

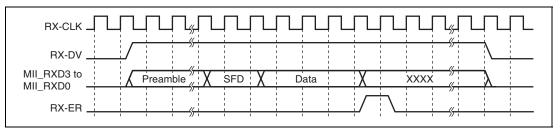

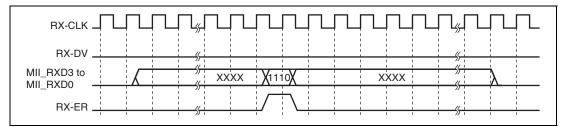

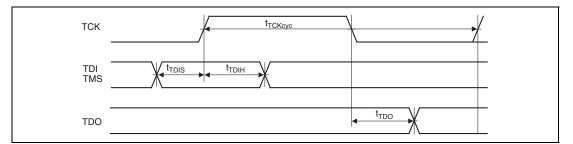

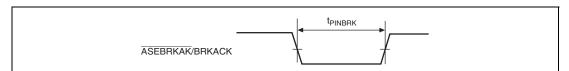

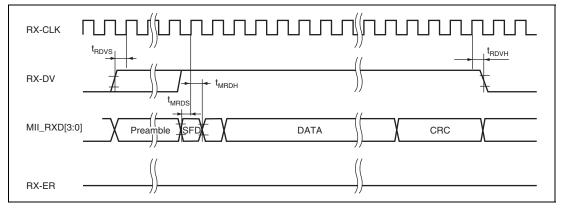

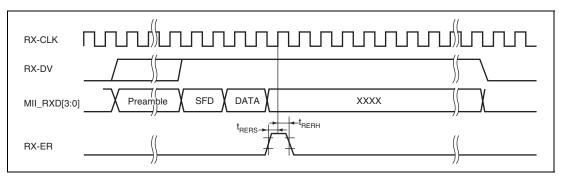

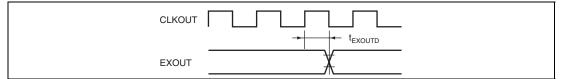

|      | 19.4.3 MII Frame Timing                                               | 745 |

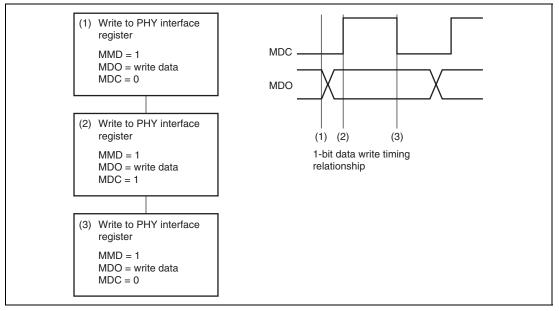

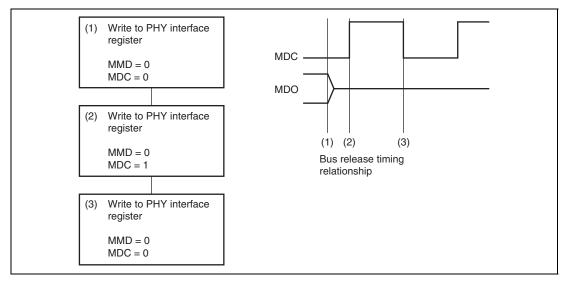

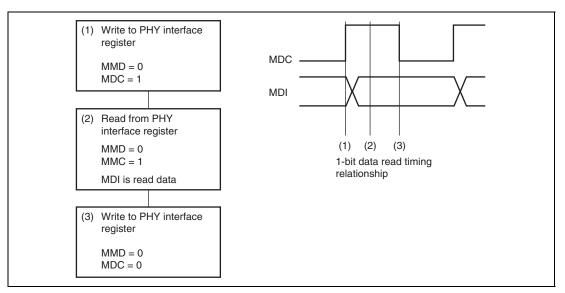

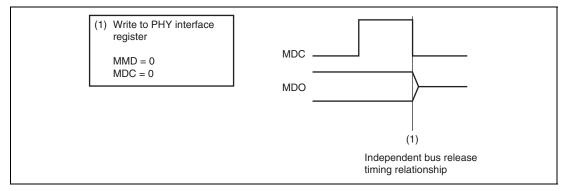

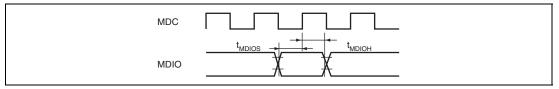

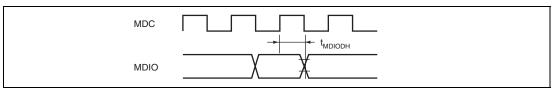

|      | 19.4.4 Accessing MII Registers                                        | 747 |

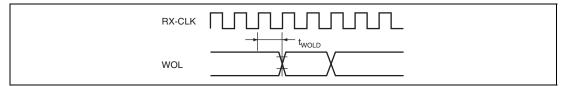

|      | 19.4.5 Magic Packet Detection                                         | 750 |

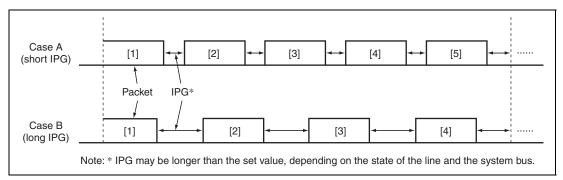

|      | 19.4.6 Operation by IPG Setting                                       | 751 |

|      | 19.4.7 Flow Control                                                   | 751 |

| 19.5 | Connection to LSI                                                     | 753 |

| 19.6 | Usage Notes                                                           | 754 |

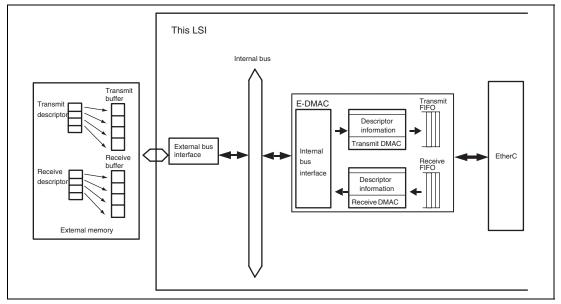

| Sect         | ion 20  | Ethernet Controller Direct Memory Access Controller        | 755 |

|--------------|---------|------------------------------------------------------------|-----|

| 20.1         |         | (E-DMAC)                                                   |     |

| 20.1<br>20.2 |         | 28                                                         |     |

|              |         | er Descriptions                                            |     |

|              |         | E-DMAC Mode Register (EDMR)                                |     |

|              |         | E-DMAC Transmit Request Register (EDTRR)                   |     |

|              |         | E-DMAC Receive Request Register (EDRRR)                    |     |

|              |         | Transmit Descriptor List Start Address Register (TDLAR)    |     |

|              |         | Receive Descriptor List Start Address Register (RDLAR)     |     |

|              |         | E-MAC/E-DMAC Status Register (EESR)                        |     |

|              |         | E-MAC/E-DMAC Status Interrupt Permission Register (EESIPR) |     |

|              |         | Transmit/Receive Status Copy Enable Register (TRSCER)      |     |

|              |         | Receive Missed-Frame Counter Register (RMFCR)              |     |

|              |         | Transmit FIFO Threshold Register (TFTR)                    |     |

|              |         | FIFO Depth Register (FDR)                                  |     |

|              |         | Receiving Method Control Register (RMCR)                   |     |

|              |         | 3 Transmit FIFO Underrun Counter (TFUCR)                   |     |

|              |         | Receive FIFO Overflow Counter (RFOCR)                      |     |

|              |         | Receive Buffer Write Address Register (RBWAR)              |     |

|              | 20.2.16 | Receive Descriptor Fetch Address Register (RDFAR)          | 784 |

|              |         | Transmit Buffer Read Address Register (TBRAR)              |     |

|              | 20.2.18 | B Transmit Descriptor Fetch Address Register (TDFAR)       | 786 |

|              | 20.2.19 | Flow Control Start FIFO Threshold Setting Register (FCFTR) | 787 |

|              | 20.2.20 | Receive Data Padding Insert Register (RPADIR)              | 789 |

|              | 20.2.21 | Transmit Interrupt Setting Register (TRIMD)                | 790 |

|              | 20.2.22 | 2 Independent Output Signal Setting Register (IOSR)        | 791 |

| 20.3         | Operati | ion                                                        | 792 |

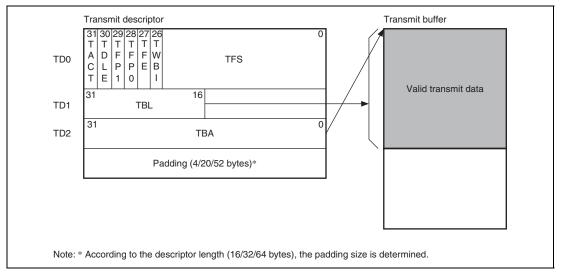

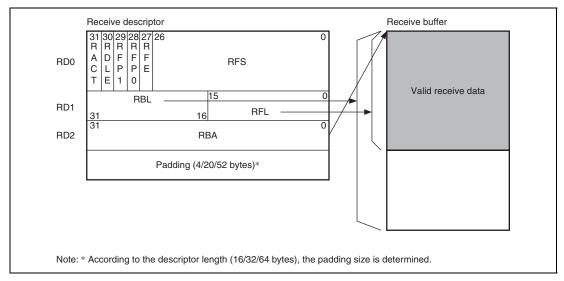

|              | 20.3.1  | Descriptor Lists and Data Buffers                          | 792 |

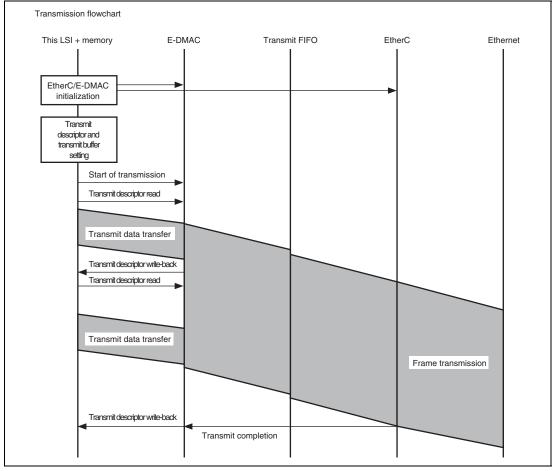

|              | 20.3.2  | Transmission                                               | 801 |

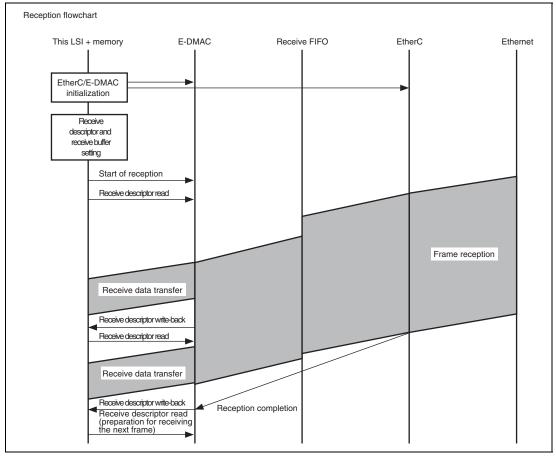

|              | 20.3.3  | Reception                                                  | 803 |

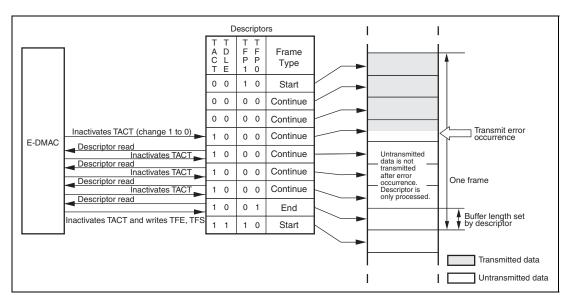

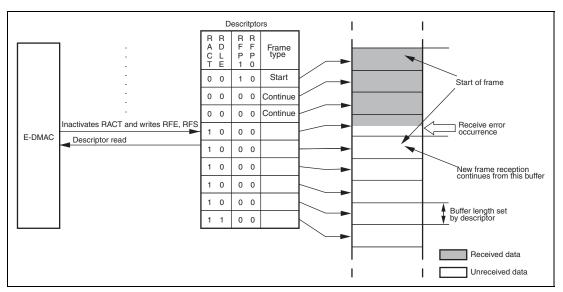

|              | 20.3.4  | Transmit/Receive Processing of Multi-Buffer Frame          |     |

|              |         | (Single-Frame/ Multi-Descriptor)                           | 805 |

| 20.4         | Usage 1 | Note                                                       | 807 |

|              | 20.4.1  | Effective Addresses in E-DMAC                              | 807 |

| Sect         | ion 21  | USB 2.0 Host/Function Module (USB)                         | 809 |

| 21.1         |         | 28                                                         |     |

| 21.2         |         | Output Pins                                                |     |

| 21.3         | -       | er Description                                             |     |

|              | _       | System Configuration Control Register (SYSCFG)             |     |

| 21.3.2   | CPU Bus Wait Setting Register (BUSWAIT)                            | 823 |

|----------|--------------------------------------------------------------------|-----|

| 21.3.3   | System Configuration Status Register (SYSSTS)                      | 824 |

| 21.3.4   | Device State Control Register (DVSTCTR)                            | 826 |

| 21.3.5   | Test Mode Register (TESTMODE)                                      | 831 |

| 21.3.6   | DMA-FIFO Bus Configuration Registers (D0FBCFG, D1FBCFG)            | 834 |

| 21.3.7   | FIFO Port Registers (CFIFO, D0FIFO, D1FIFO)                        | 835 |

| 21.3.8   | FIFO Port Select Registers (CFIFOSEL, D0FIFOSEL, D1FIFOSEL)        | 838 |

| 21.3.9   | FIFO Port Control Registers (CFIFOCTR, D0FIFOCTR, D1FIFOCTR)       | 845 |

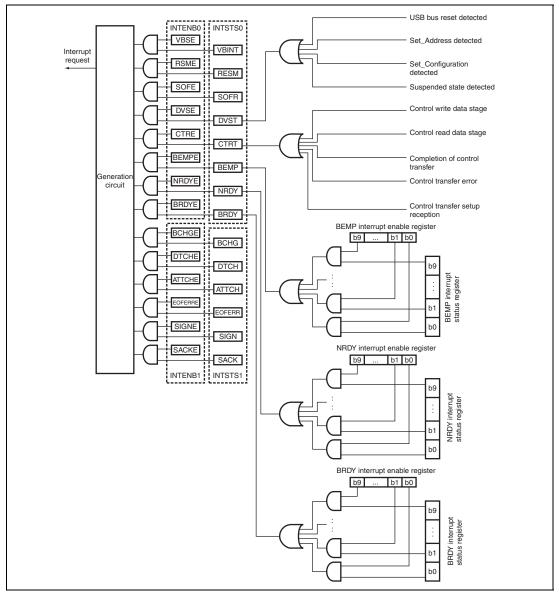

| 21.3.10  | Interrupts Enable Register 0 (INTENB0)                             | 849 |

| 21.3.11  | Interrupt Enable Register 1 (INTENB1)                              | 851 |

| 21.3.12  | BRDY Interrupt Enable Register (BRDYENB)                           | 853 |

|          | NRDY Interrupt Enable Register (NRDYENB)                           |     |

| 21.3.14  | BEMP Interrupt Enable Register (BEMPENB)                           | 857 |

| 21.3.15  | SOF Control Register (SOFCFG)                                      | 859 |

| 21.3.16  | Interrupt Status Register 0 (INTSTS0)                              | 860 |

| 21.3.17  | Interrupt Status Register 1 (INTSTS1)                              | 866 |

| 21.3.18  | BRDY Interrupt Status Register (BRDYSTS)                           | 872 |

| 21.3.19  | NRDY Interrupt Status Register (NRDYSTS)                           | 874 |

| 21.3.20  | BEMP Interrupt Status Register (BEMPSTS)                           | 876 |

| 21.3.21  | Frame Number Register (FRMNUM)                                     | 877 |

| 21.3.22  | uFrame Number Register (UFRMNUM)                                   | 880 |

| 21.3.23  | USB Address Register (USBADDR)                                     | 881 |

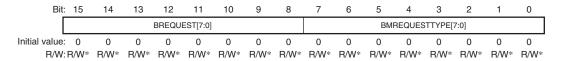

| 21.3.24  | USB Request Type Register (USBREQ)                                 | 882 |

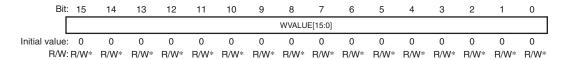

| 21.3.25  | USB Request Value Register (USBVAL)                                | 884 |

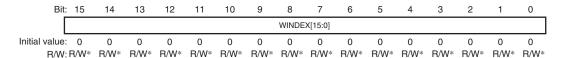

|          | USB Request Index Register (USBINDX)                               |     |

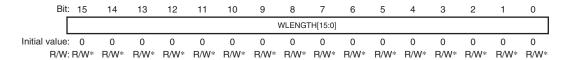

| 21.3.27  | USB Request Length Register (USBLENG)                              | 886 |

| 21.3.28  | DCP Configuration Register (DCPCFG)                                | 887 |

| 21.3.29  | DCP Maximum Packet Size Register (DCPMAXP)                         | 888 |

| 21.3.30  | DCP Control Register (DCPCTR)                                      | 889 |

| 21.3.31  | Pipe Window Select Register (PIPESEL)                              | 899 |

| 21.3.32  | Pipe Configuration Register (PIPECFG)                              | 900 |

| 21.3.33  | Pipe Buffer Setting Register (PIPEBUF)                             | 907 |

|          | Pipe Maximum Packet Size Register (PIPEMAXP)                       |     |

| 21.3.35  | Pipe Timing Control Register (PIPEPERI)                            | 912 |

| 21.3.36  | PIPEn Control Registers (PIPEnCTR) (n = 1 to 9)                    | 914 |

| 21.3.37  | PIPEn Transaction Counter Enable Registers (PIPEnTRE) (n = 1 to 5) | 934 |

| 21.3.38  | PIPEn Transaction Counter Registers (PIPEnTRN) (n = 1 to 5)        | 936 |

| 21.3.39  | Device Address n Configuration Registers (DEVADDn) (n = 0 to A)    | 938 |

| Operatio | on                                                                 | 941 |

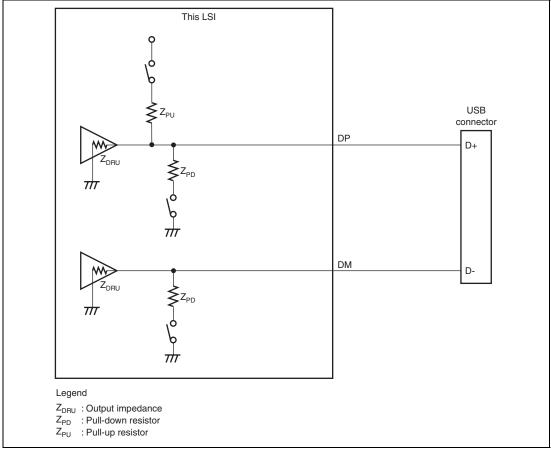

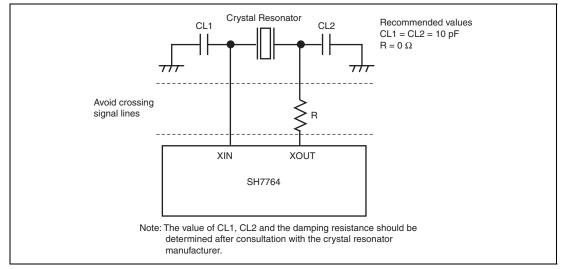

| 21.4.1   | System Control and Oscillation Control                             | 941 |

|          |                                                                    |     |

21.4

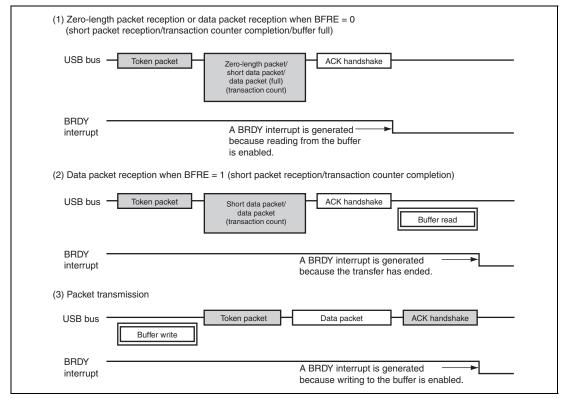

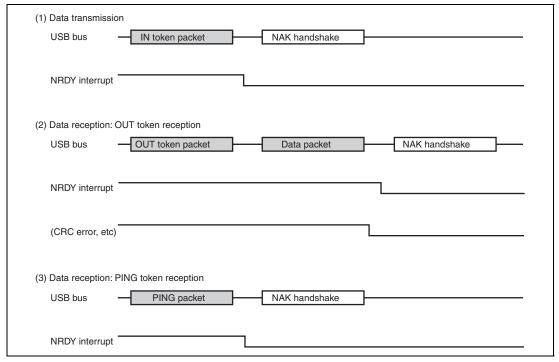

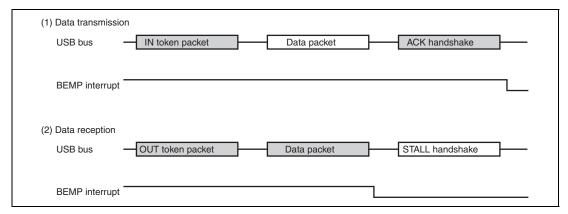

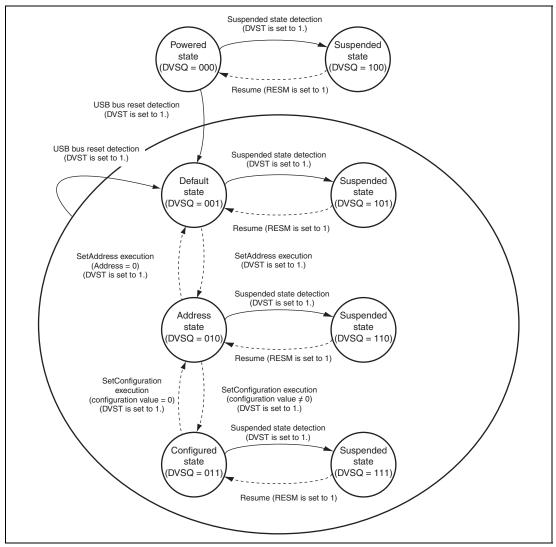

|       | 21.4.2  | Interrupt Functions                                               | 943   |

|-------|---------|-------------------------------------------------------------------|-------|

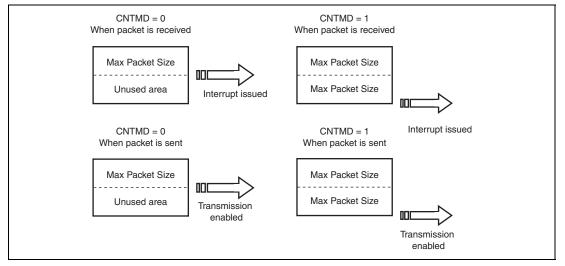

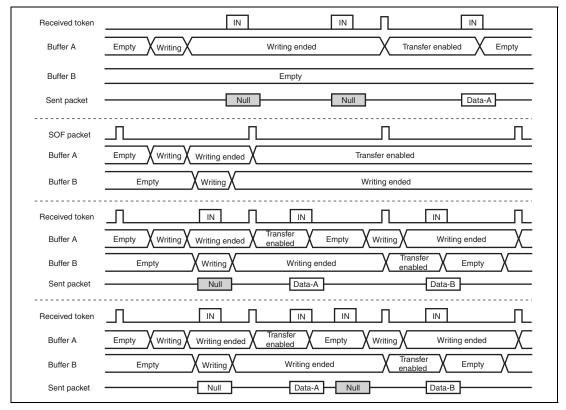

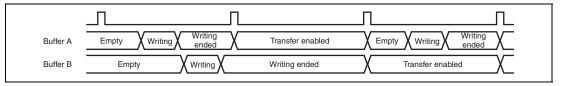

|       | 21.4.3  | Pipe Control                                                      | 967   |

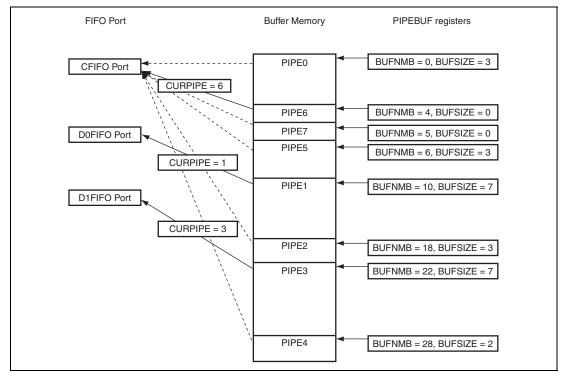

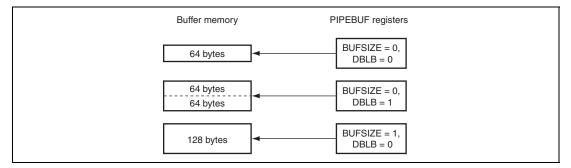

|       | 21.4.4  | FIFO Buffer Memory                                                | 977   |

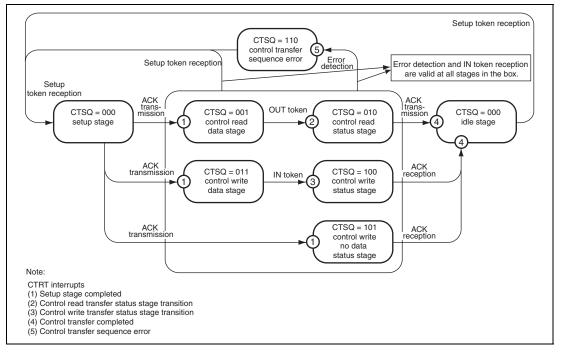

|       | 21.4.5  | Control Transfers (DCP)                                           | 987   |

|       | 21.4.6  | Bulk Transfers (PIPE1 to PIPE5)                                   | 991   |

|       | 21.4.7  | Interrupt Transfers (PIPE6 to PIPE9)                              | 993   |

|       | 21.4.8  | Isochronous Transfers (PIPE1 and PIPE2)                           | 994   |

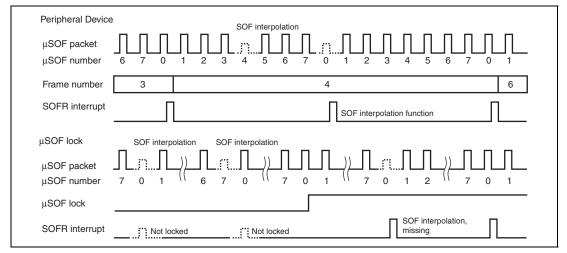

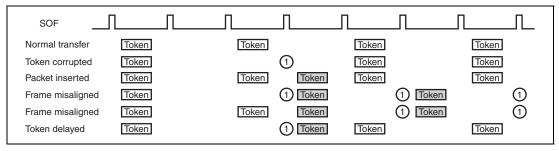

|       | 21.4.9  | SOF Interpolation Function                                        | 1005  |

|       | 21.4.10 | Pipe Schedule                                                     | 1006  |

| 21.5  | Usage 1 | Notes                                                             | 1008  |

|       | 21.5.1  | USB Startup and Stop Procedures                                   | 1008  |

|       | 21.5.2  | Notes on USB Clock Peripheral Circuit Design                      | 1009  |

|       | 21.5.3  | Handling of VBUS Pin                                              | 1010  |

|       | 21.5.4  | Usage Precautions of USB Disconnection Process at the Time of     |       |

|       |         | Using the Function Controller Function and Full-Speed Operations  | 1010  |

| Secti | ion 22  | LCD Controller (LCDC)                                             | .1013 |

| 22.1  |         | ·S                                                                |       |

| 22.2  |         | Output Pins                                                       |       |

| 22.3  | Registe | er Configuration                                                  | 1016  |

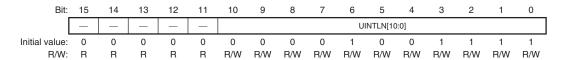

|       | 22.3.1  | LCDC Input Clock Register (LDICKR)                                | 1019  |

|       | 22.3.2  | LCDC Module Type Register (LDMTR)                                 | 1021  |

|       | 22.3.3  | LCDC Data Format Register (LDDFR)                                 | 1024  |

|       | 22.3.4  | LCDC Start Address Register for Upper Display Data Fetch (LDSARU) | 1026  |

|       | 22.3.5  | LCDC Start Address Register for Lower Display Data Fetch (LDSARL) | 1027  |

|       | 22.3.6  | LCDC Line Address Offset Register for Display Data Fetch (LDLAOR) | 1028  |

|       | 22.3.7  | LCDC Palette Control Register (LDPALCR)                           | 1029  |

|       | 22.3.8  | Palette Data Registers 00 to FF (LDPR00 to LDPRFF)                | 1030  |

|       | 22.3.9  | LCDC Horizontal Character Number Register (LDHCNR)                | 1031  |

|       | 22.3.10 | LCDC Horizontal Sync Signal Register (LDHSYNR)                    | 1032  |

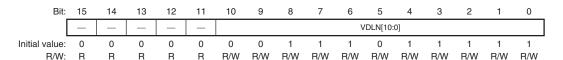

|       | 22.3.11 | LCDC Vertical Display Line Number Register (LDVDLNR)              | 1033  |

|       | 22.3.12 | LCDC Vertical Total Line Number Register (LDVTLNR)                | 1034  |

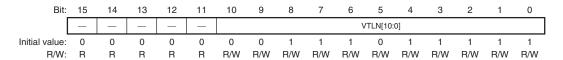

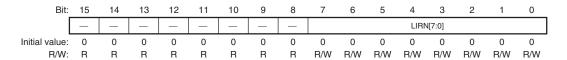

|       |         | LCDC Vertical Sync Signal Register (LDVSYNR)                      |       |

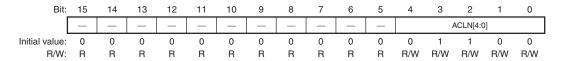

|       | 22.3.14 | LCDC AC Modulation Signal Toggle Line Number Register (LDACLNR)   | 1036  |

|       |         | LCDC Interrupt Control Register (LDINTR)                          |       |

|       |         | LCDC Power Management Mode Register (LDPMMR)                      |       |

|       |         | LCDC Power-Supply Sequence Period Register (LDPSPR)               |       |

|       |         | LCDC Control Register (LDCNTR)                                    |       |

|       |         | LCDC User Specified Interrupt Control Register (LDUINTR)          |       |

|       | 22.3.20 | LCDC User Specified Interrupt Line Number Register (LDUINTLNR)    | 1047  |

|      | 22.3.21           | LCDC Memory Access Interval Number Register (LDLIRNR)     | 1048 |

|------|-------------------|-----------------------------------------------------------|------|

| 22.4 | Operation         |                                                           |      |

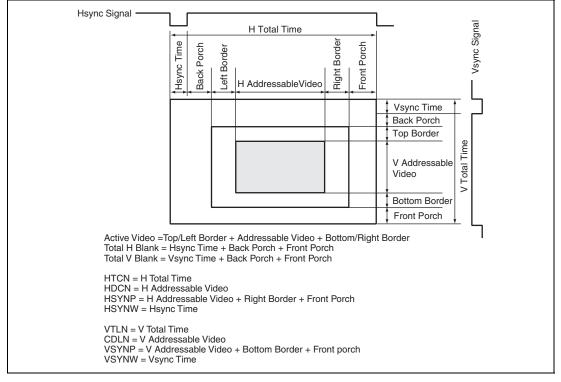

|      | 22.4.1            | LCD Module Sizes which can be Displayed in this LCDC      | 1049 |

|      | 22.4.2            | Color Palette Specification                               | 1051 |

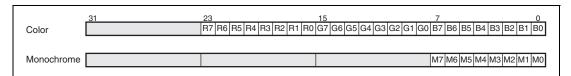

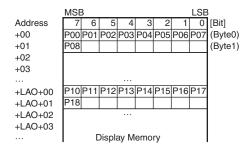

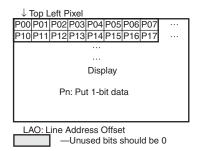

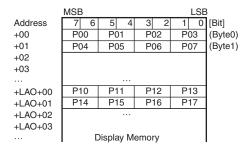

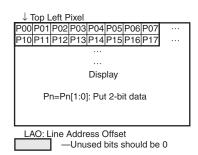

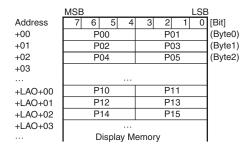

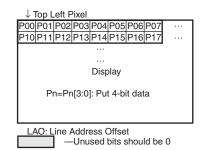

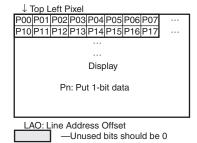

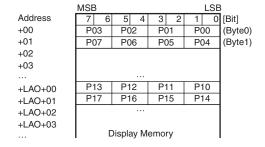

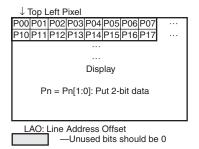

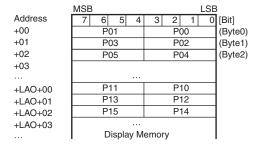

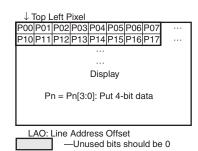

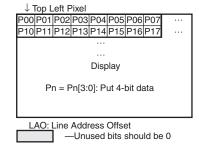

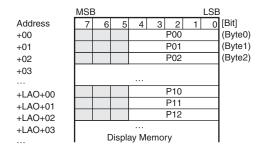

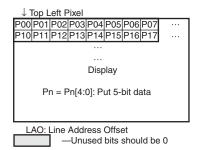

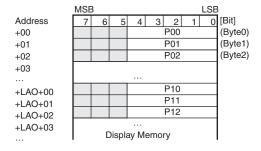

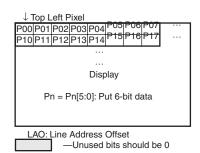

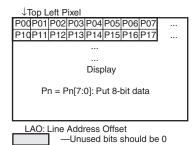

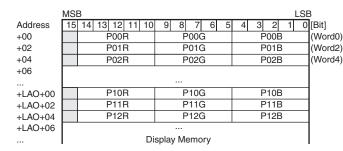

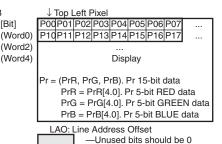

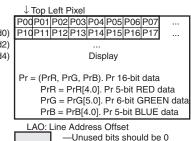

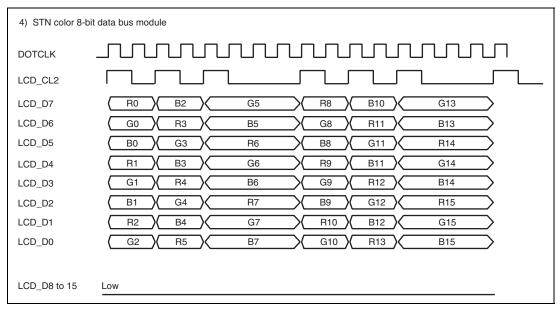

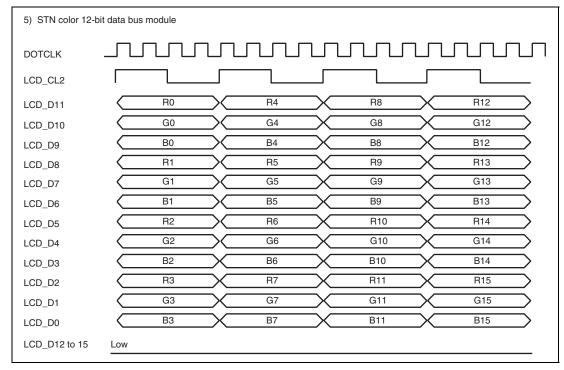

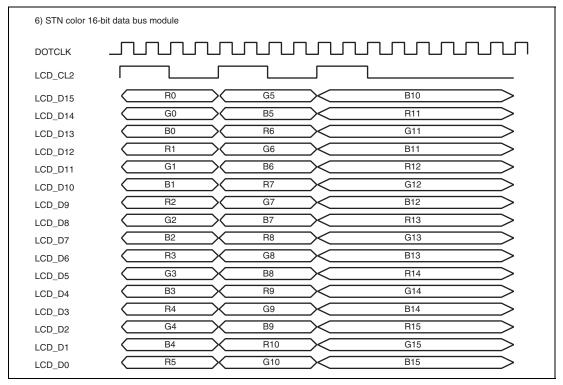

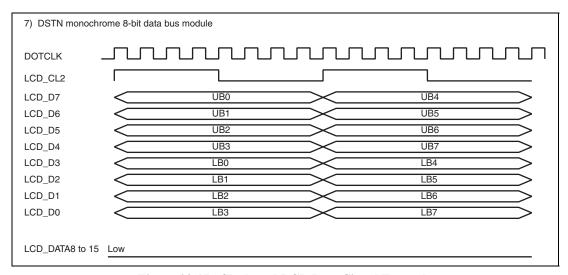

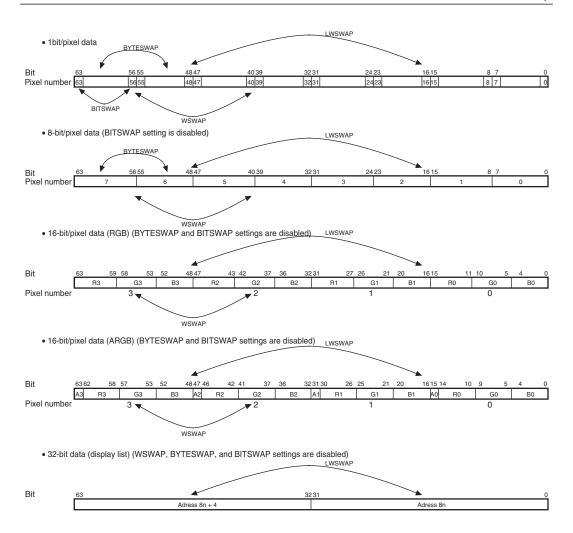

|      | 22.4.3            | Data Format                                               | 1052 |

|      | 22.4.4            | Setting the Display Resolution                            | 1056 |

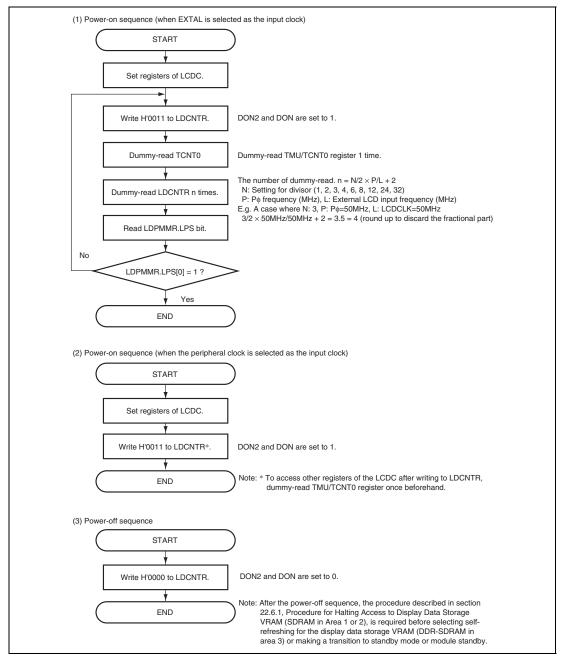

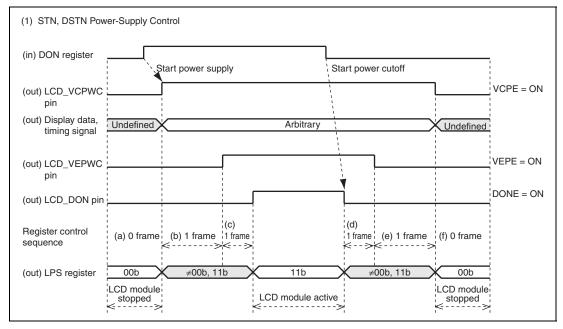

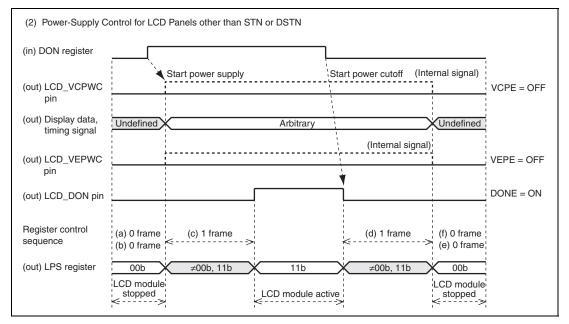

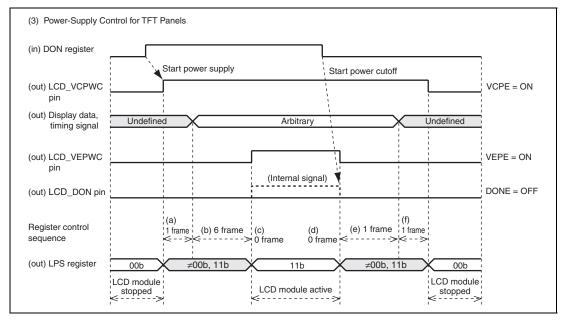

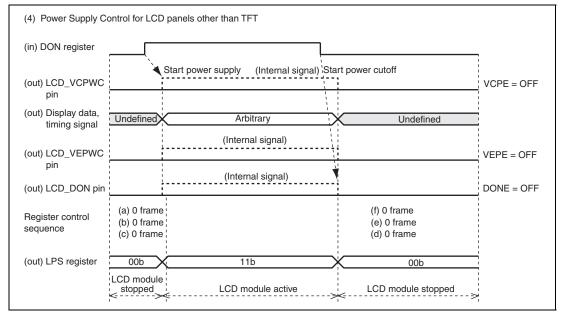

|      |                   | Power-Supply Control Sequence                             |      |

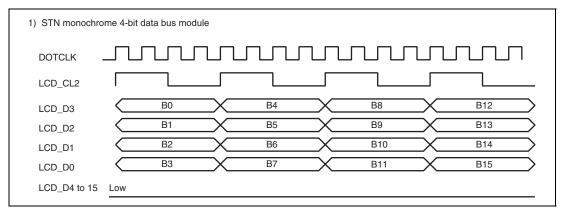

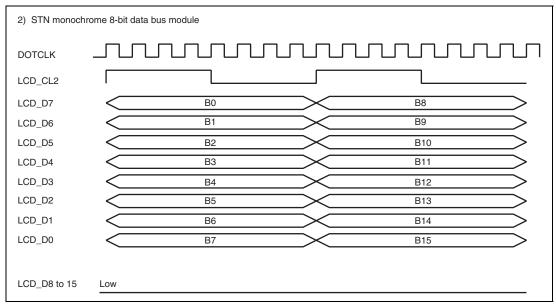

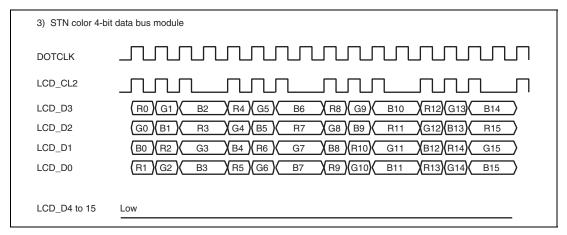

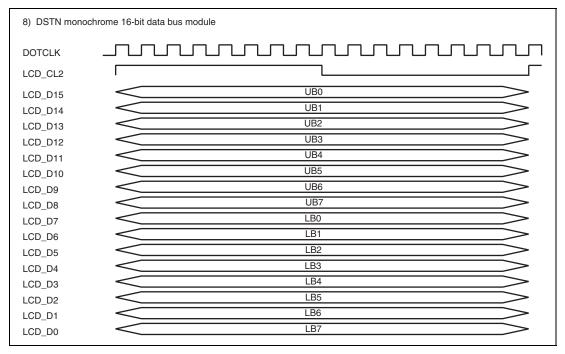

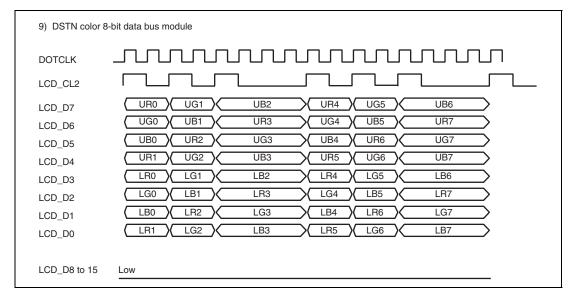

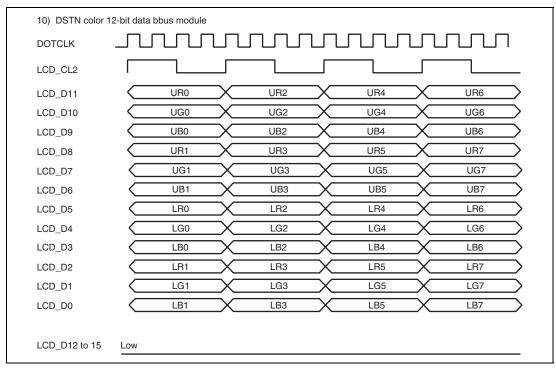

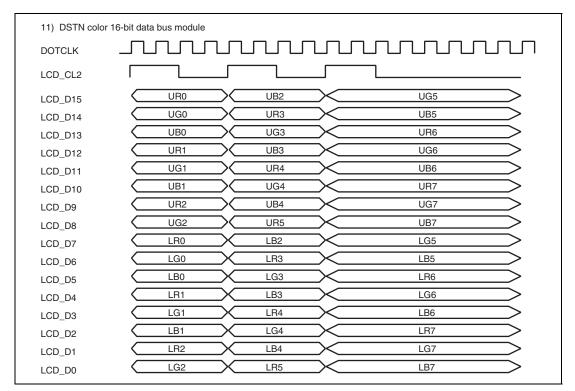

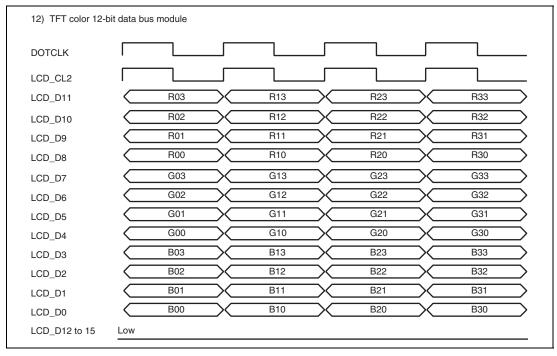

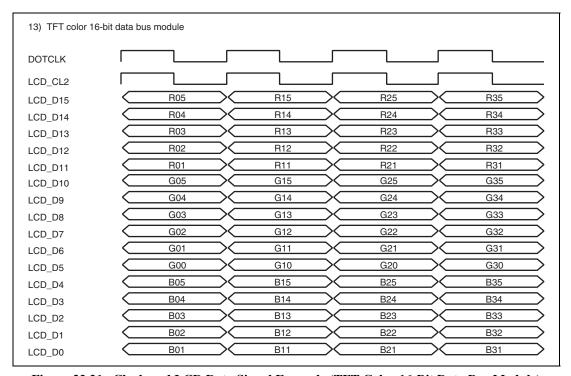

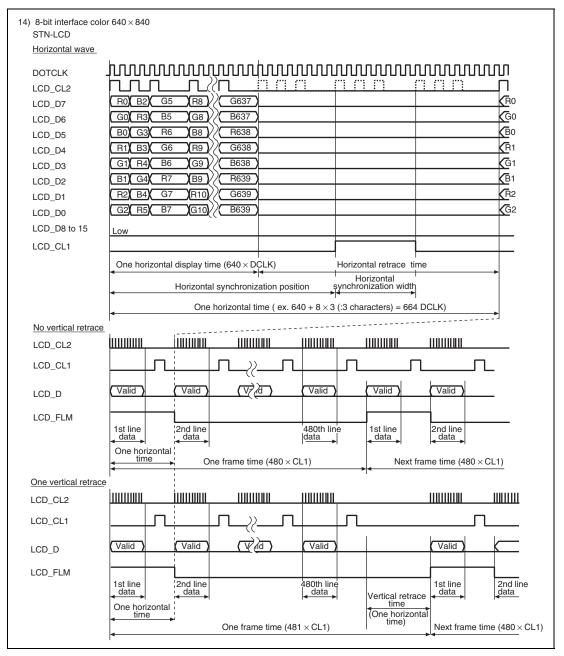

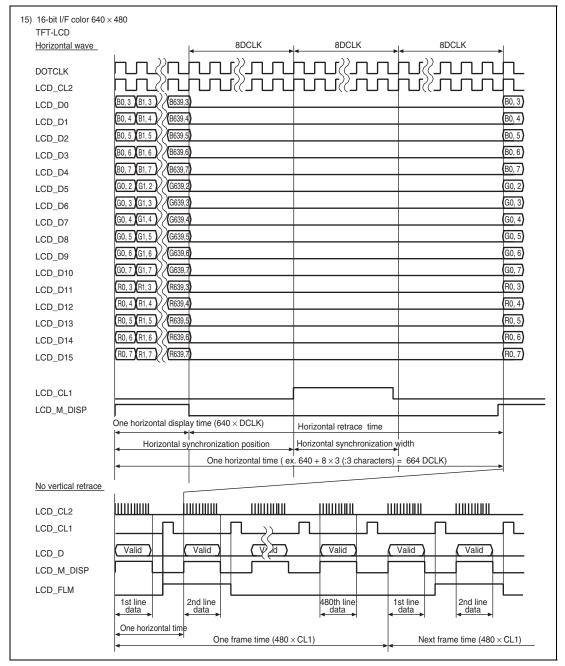

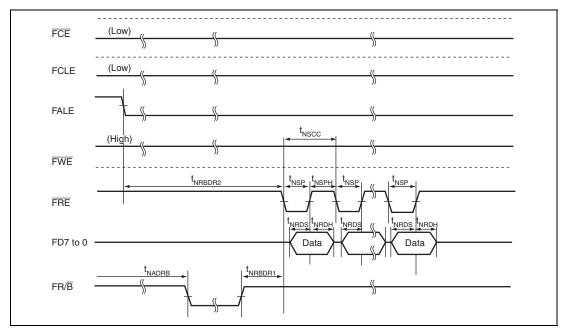

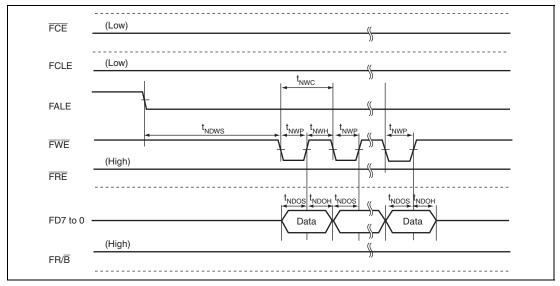

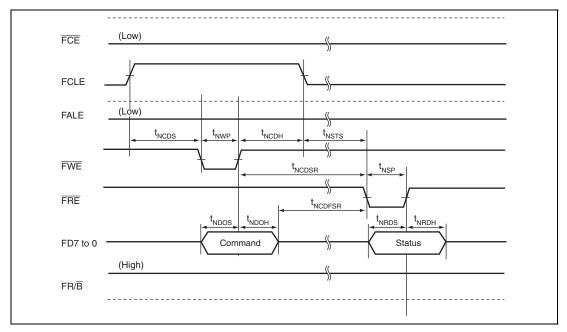

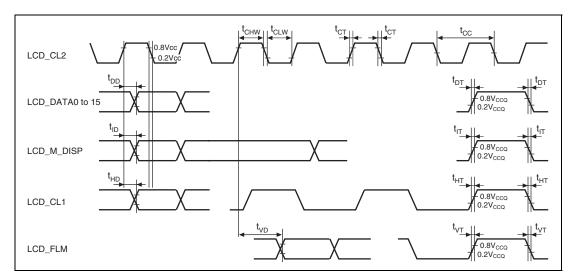

| 22.5 | Clock             | and LCD Data Signal Examples                              | 1063 |

| 22.6 | Usage             | Notes                                                     | 1076 |

|      | 22.6.1            | Procedure for Halting Access to Display Data Storage VRAM |      |

|      |                   | (SDRAM in Area 1 or 2)                                    | 1076 |

|      | 22.6.2            | Notes on Holding the Access Request by MCU                | 1076 |

| Sect | ion 23            | G2D                                                       | 1077 |

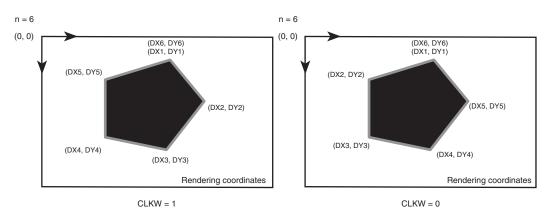

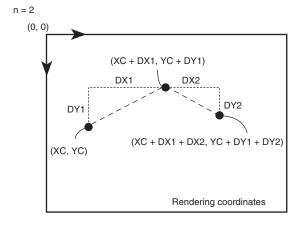

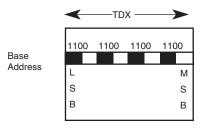

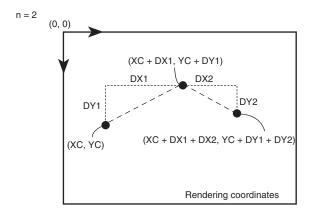

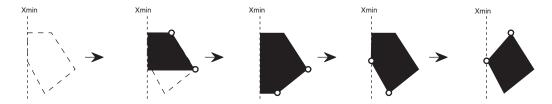

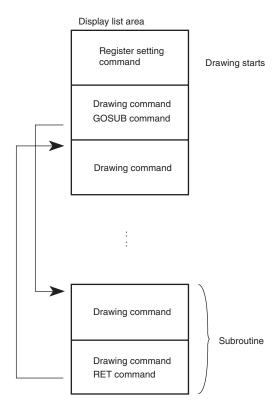

| 23.1 | Basic I           | Functions                                                 | 1077 |

|      | 23.1.1            | List of Commands and Rendering Attributes                 | 1077 |

|      |                   | Basic Functions                                           |      |

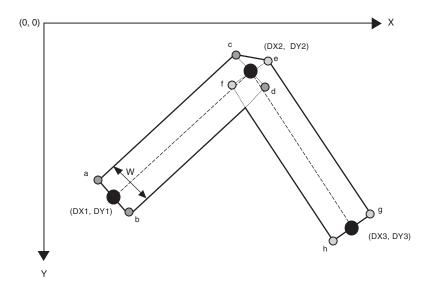

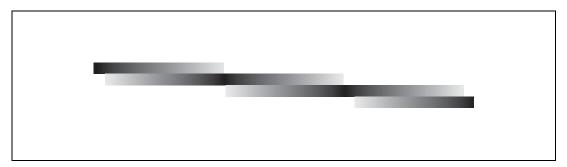

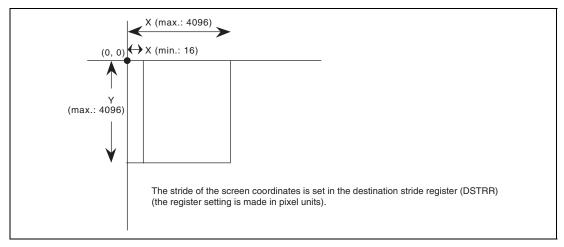

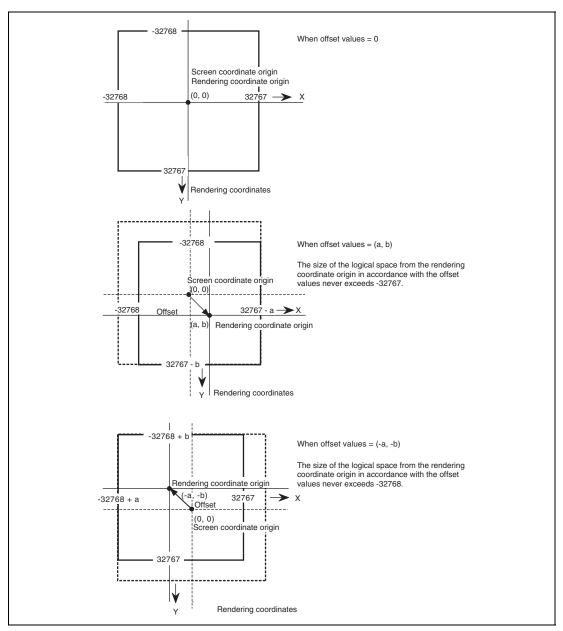

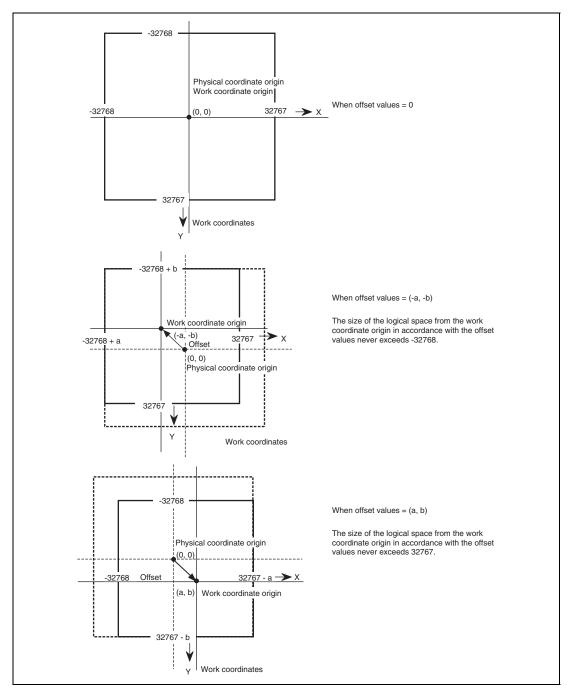

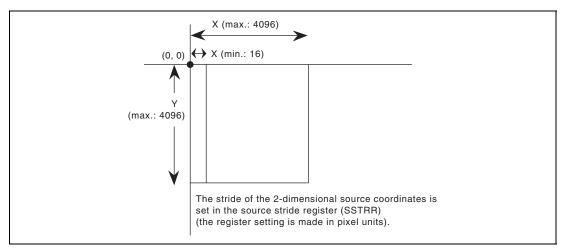

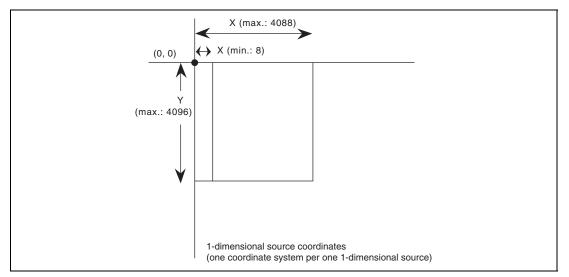

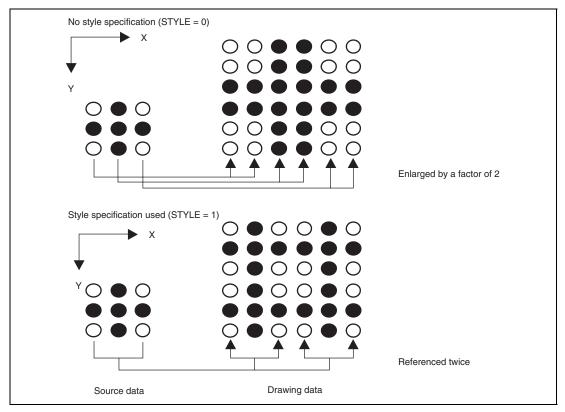

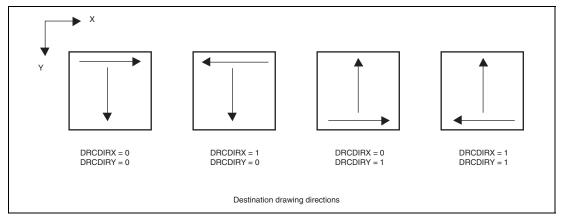

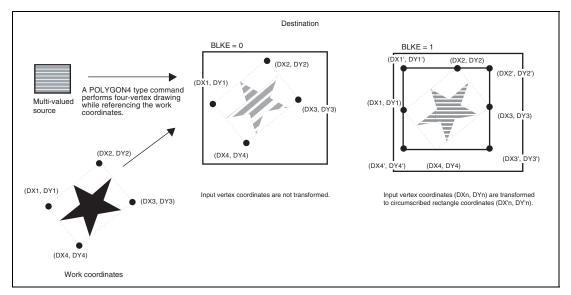

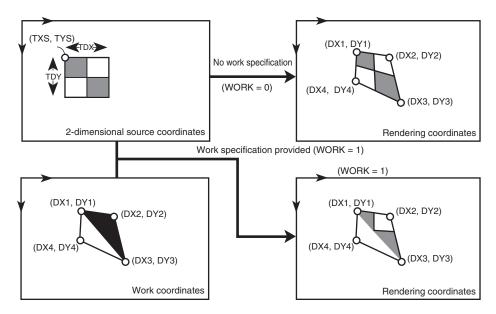

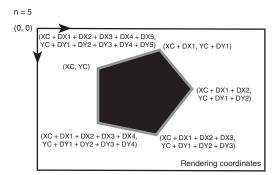

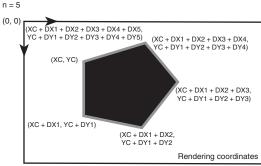

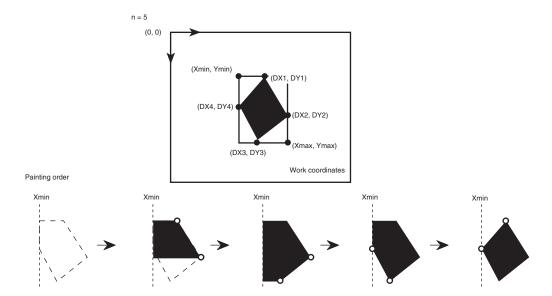

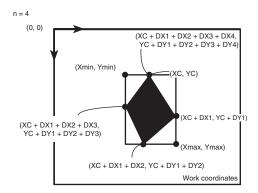

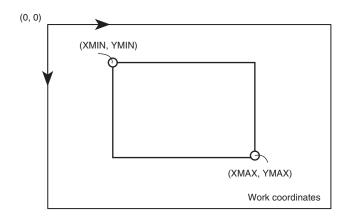

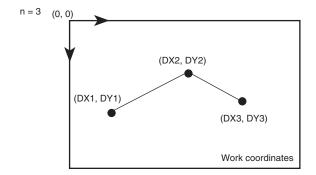

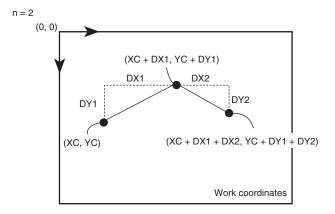

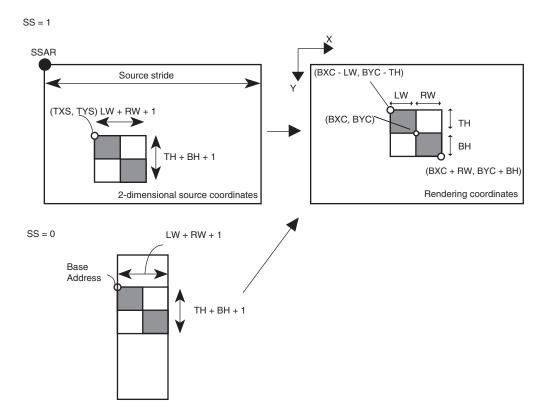

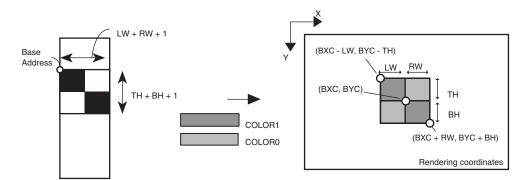

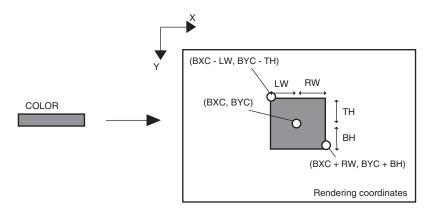

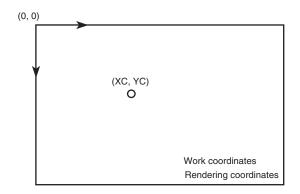

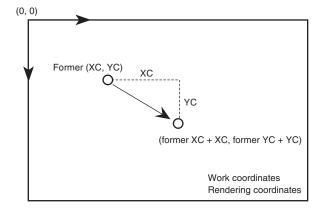

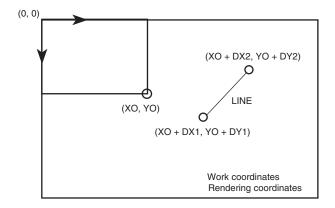

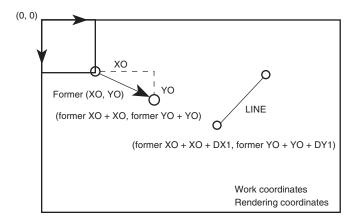

|      |                   | Coordinate Systems                                        |      |

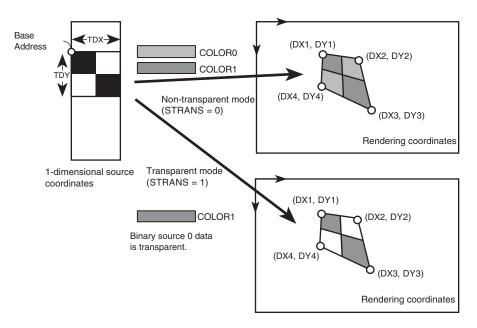

|      | 23.1.4            | Data Formats                                              | 1095 |

|      |                   | Rendering Attributes                                      |      |

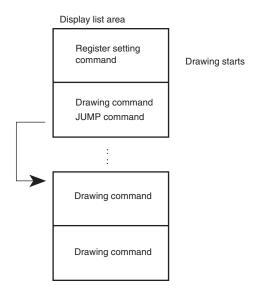

| 23.2 |                   | y List                                                    |      |

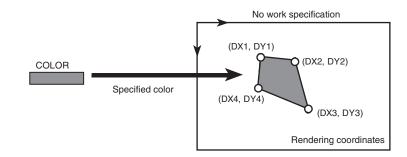

|      | 23.2.1            | 4-Vertex Screen Drawing Commands                          | 1109 |

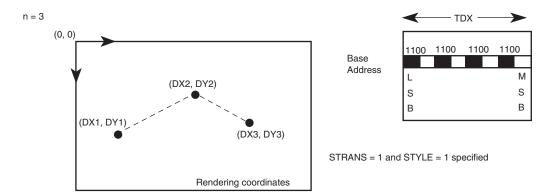

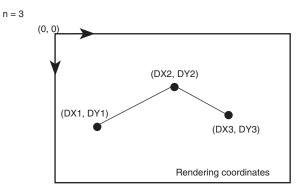

|      |                   | Line Drawing Commands                                     |      |

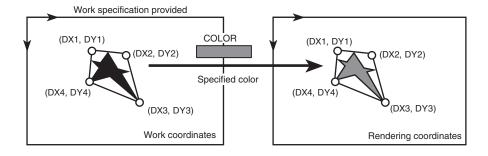

|      |                   | Work Screen Drawing Commands                              |      |

|      |                   | Work Line Drawing Commands                                |      |

|      |                   | Rectangle Drawing Commands                                |      |

|      | 23.2.6            | Control Commands                                          | 1178 |

| 23.3 |                   | er Specifications                                         |      |

|      | 23.3.1            | -                                                         |      |

|      | 23.3.2            | Memory Control Registers                                  | 1207 |

|      | 23.3.3            | Color Control Registers                                   | 1212 |

|      | 23.3.4            | Rendering Control Registers                               | 1215 |

|      |                   | Coordinate Transformation Control Registers               |      |

| 23.4 | Usage             | Notes                                                     | 1231 |

|      | 23.4.1            | G2D Command Restriction                                   | 1231 |

| Sect | ion 24            | Video Display Controller (VDC2)                           | 1233 |

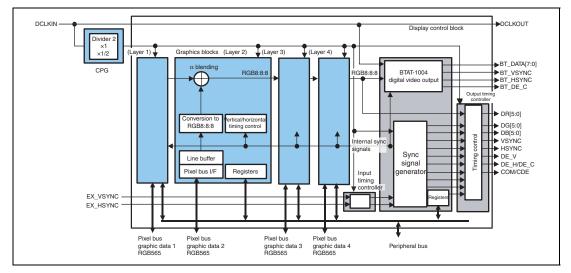

| 24.1 |                   | ew                                                        |      |

| 24.2 |                   | es                                                        |      |

| 24.3 | Input/Output Pins |                                                           |      |

| 24.4 | VDC2                  | Configuration                                                   | . 1236 |  |

|------|-----------------------|-----------------------------------------------------------------|--------|--|

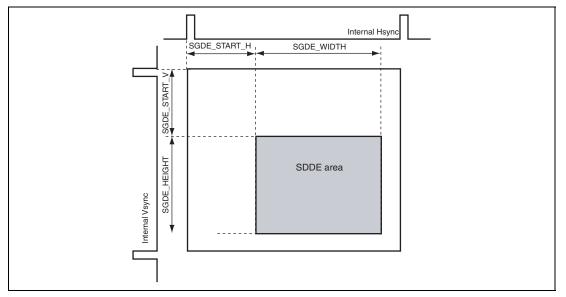

| 24.5 | Functio               | nal Descriptions                                                | . 1238 |  |

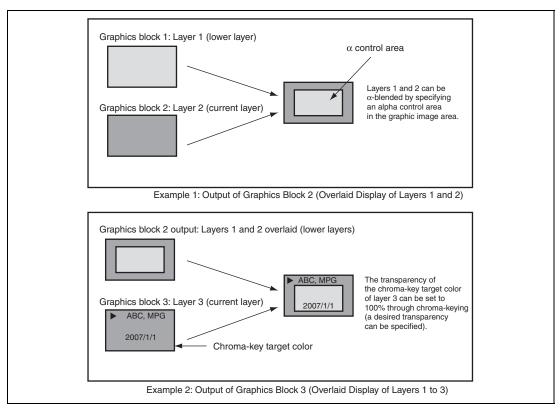

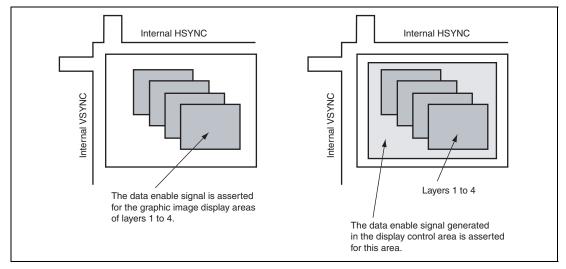

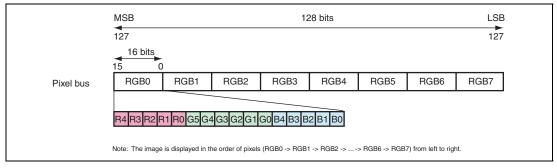

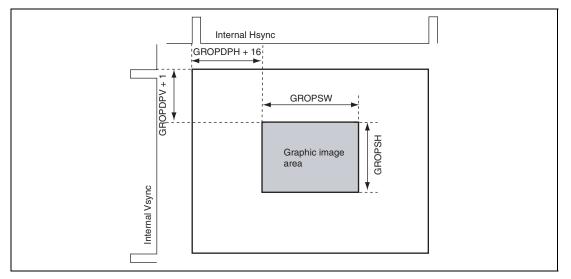

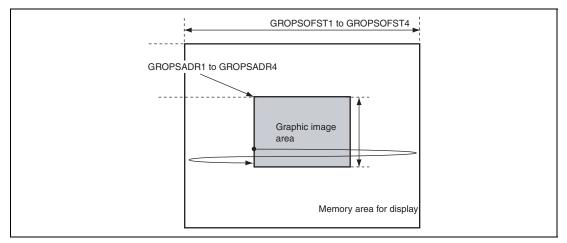

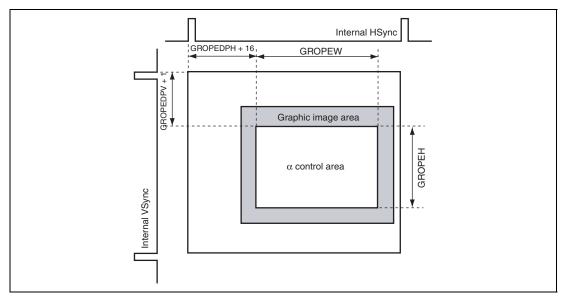

|      | 24.5.1                | Graphics (Layers 1 to 4)                                        | . 1238 |  |

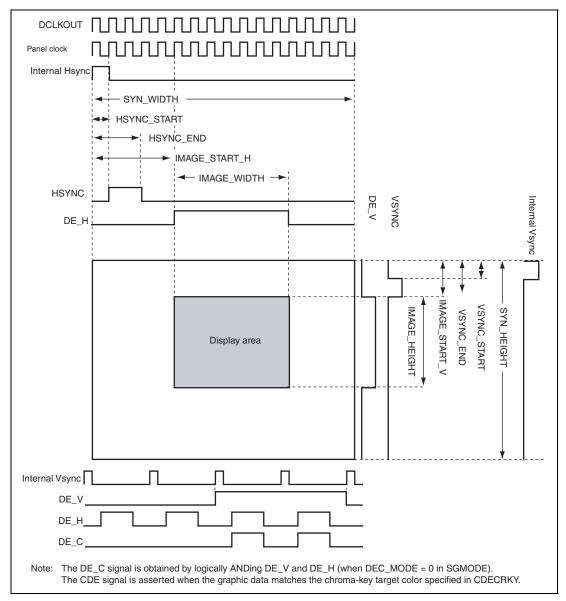

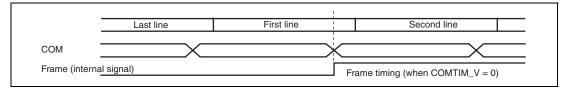

|      | 24.5.2                | Sync Signal Generation                                          | . 1239 |  |

|      | 24.5.3                | External Sync Mode                                              | . 1241 |  |

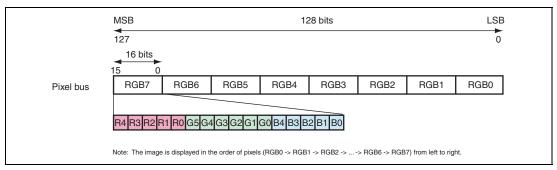

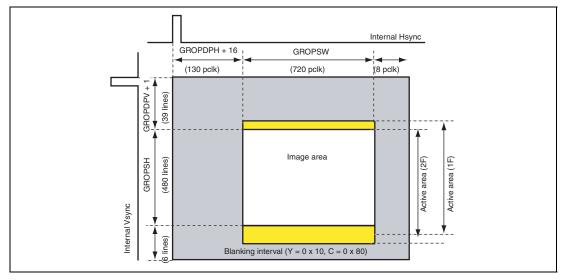

|      | 24.5.4                | Digital Video Output                                            | . 1241 |  |

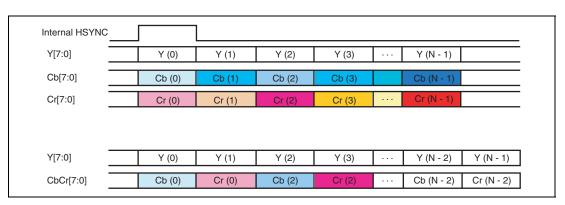

|      | 24.5.5                | Conversion from RGB565 to YC444                                 | . 1242 |  |

|      | 24.5.6                | Conversion from YC444 to YC422                                  | . 1242 |  |

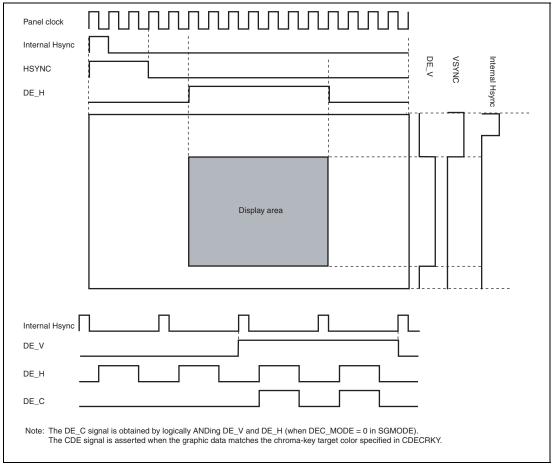

|      | 24.5.7                | Data Enable Signal (Composite)                                  | . 1243 |  |

| 24.6 | Register Descriptions |                                                                 |        |  |

|      | 24.6.1                | Graphics Block Control Registers (GRCMEN1 to GRCMEN4)           | 1250   |  |